MIPI MPHY 6.0: Enabling Next-Generation UFS Performance

High-speed chip-to-chip data transfer is continuously evolving to meet increasing performance demands. MIPI MPHY is a high-speed physical layer interface developed by the MIPI Alliance. This protocol is used for high-speed chip-to-chip interfaces, mainly in mobile and automotive devices.

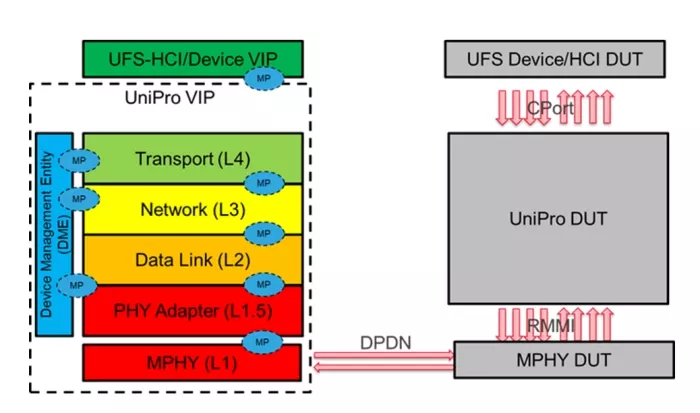

MPHY serves as the physical layer for the MIPI UniPro transport layer. The MPHY+UniPro stack is used with the JEDEC-defined UFS application layer protocol. UFS is used in flash memory-based storage and with other high-bandwidth applications. Though UniPro was initially intended for use with almost all devices in mobile applications (such as cameras, displays, etc.) and is an application agnostic transport layer, currently, it is mainly being used with UFS for all applications.

While MPHY 6.0 maintains backward compatibility with previous versions, it has made a few significant changes to increase the data rate and improve performance.

- To meet the demand for higher speeds in mobile applications and inter-processor communications, MPHY 6.0 has added a new High-Speed Gear 6 (HS-G6), which supports data rates double those of the previous maximum data rate of HS-G5.

- Data transfer capabilities are advanced with Pulse Amplitude Modulation 4 (PAM4) signaling and 1b1b encoding.

- While PAM4 signaling increases data rate, it has a higher sensitivity to noise. Accordingly, MPHY 6.0 incorporates enhanced receiver features, such as Forward Error Correction (FEC) capable of correcting up to 3 bytes of data.

- Another challenge with increased data rate was Inter Symbol Interference (ISI), where the signal from one bit will overlap with other bit. This makes it difficult for the receiver to distinguish between the bits. To address this, transmitter equalization was introduced in MPHY 6.0. With this support, M-TX can utilize channel equalization in the form of de-emphasis and pre-shoot. This was introduced for the data rates HS-G4 and above.

MIPI UniPro 3.0 was developed to work with MPHY 6.0. UniPro allows flexible and scalable configurations to support scalable bandwidth and end-to-end flow control.

With the Cadence Verification IP for MIPI MPHY 6.0 and MIPI UniPro 3.0 now available, early adopters can start working with the provisional specification immediately, ensuring compliance with the standard and achieving the fastest path to IP and SoC verification closure.

For any additional clarification or technical assistance, users are encouraged to reach out through talk_to_vip_expert@cadence.com

For more information, please visit https://www.cadence.com/en_US/home/tools/system-design-and-verification/verification-ip/simulation-vip.html

Related Semiconductor IP

- Simulation VIP for MIPI M-PHY

- MIPI M-PHY HS Gear 4 IP

- MIPI M-PHY IP

- MIPI M-PHY Verification IP

- MIPI M-PHY

Related Blogs

- Altera's Next-Generation FPGAs: Advanced Process Lithographies Lead to Performance, Power Consumption Efficiencies

- How did JEDEC UFS beat the MIPI CSI3 and DSI2 in adoption race?

- Technical Comparison: MIPI MPHY 3.1 vs MPHY 3.0

- MIPI MPHY "CheckMate" Verification IP - An Introduction

Latest Blogs

- Considerations When Architecting Your Next SoC: NoCs with Arteris

- Implementing Dual-core Lockstep in the CHIPS Alliance VeeR EL2 RISC-V core for safety-critical applications

- Rethinking Display Safety: Why RISC-V-Supervised DisplayPort Subsystems Enable Secure, Isolated Automotive Architectures

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling