Coprocessor IP

Welcome to the ultimate Coprocessor IP hub! Explore our vast directory of Coprocessor IP

All offers in

Coprocessor IP

Filter

Compare

33

Coprocessor IP

from

9

vendors

(1

-

10)

-

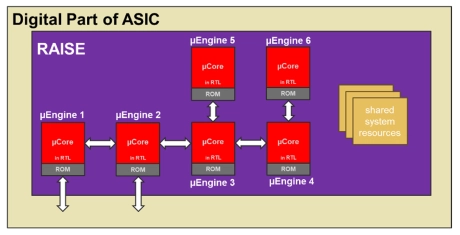

Configurable CPU tailored precisely to your needs

- Increased efficiency by converting digital design into software development

- Hardware independent and parallel Software development

- Rapid system development and evaluation:

- Software debug and tests with RAISE Simulator

-

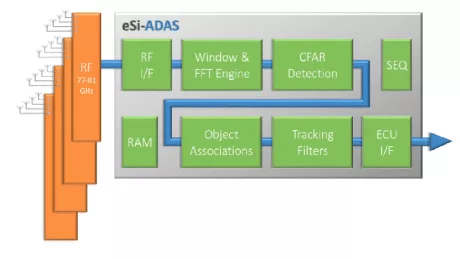

Radar processing IP suite for Advanced Driver Assistance Systems

- The eSi-ADAS™ is a suite of radar accelerator IP including a complete Radar co-processor engine, they enhance the overall performance and capabilities of radar systems for automotive, drone and UAV applications that require fast and responsive situational awareness.

- The IP has been licensed to some of the leading automotive Tier 1 and Tier 2 suppliers and is in production vehicles.

-

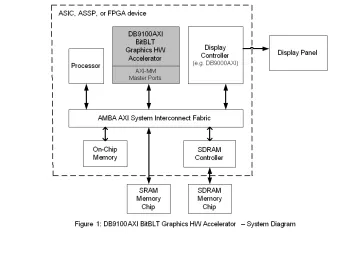

BitBLT Graphics Hardware Accelerator (AXI Bus)

- The DB9100AXI BitBLT Graphics Hardware Accelerator Verilog IP Core renders a graphics frame by generating new bitmaps from commands to combining existing bitmaps on and off-screen using one of 256 Raster Operations.

- A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT).

- The DB9100AXI also contains a Monochrome Bitmap Color Expansion feature, typically used for font expansion of compressed character bitmaps. A 1-bit depth bitmap is expanded to one of two colors, a foreground or background color, with the foreground color representing the text, and the background color the non-text background.

-

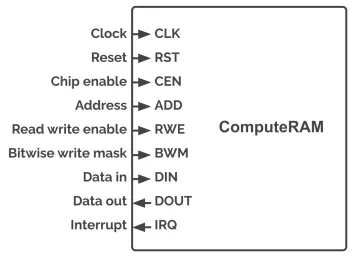

ComputeRAM

- Available as a 18 kB macro in GlobalFoundries 22FDX process; - Memory Compiler and FinFET variants under development

- Low power sleep mode with data retention

- Built using proven foundry SRAM bit cells, fully CMOS, strictly obeys foundry DFM/DRC rules

- Bit-accurate computation

-

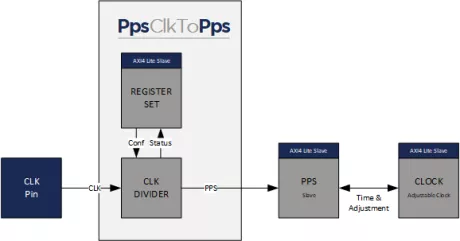

Pulse Per Second (PPS) Clock to PPS core

- Configurable input frequency from 100Hz to 100MHz

- Input frequency supervision

- PPS duty cycle configurable in ms steps

- PPS Generation runs directly on Input Clock (minimal Jitter)

-

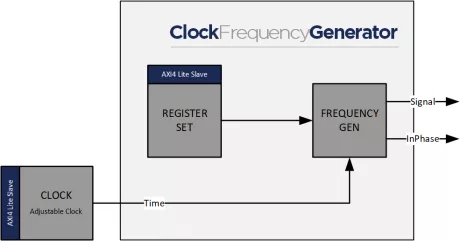

Time aligned Frequency Generator core

- Configurable frequency signal generation (0-10MHz) in 1Hz steps

- Configurable polarity

- Output delay compensation

-

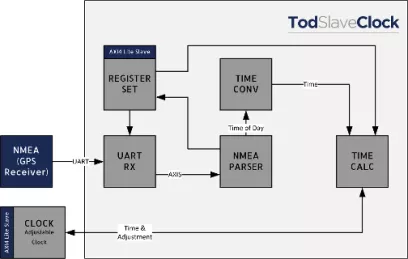

NMEA Time of Day (ToD) Slave core

- Time of Day Slave Clock

- Built-in UART receiver with configurable baud rate

- NMEA message parser

- Support for NMEA GPZDA and GPRMC messages for time extraction

-

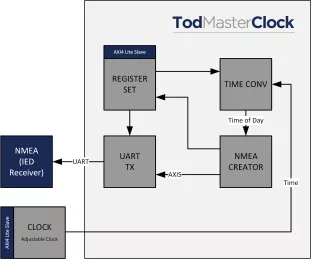

NMEA Time of Day (ToD) Master core

- Time of Day Master Clock

- Built-in UART transmitter with configurable baud rate

- NMEA message creator

- Support for NMEA GPZDA messages for time distribution

-

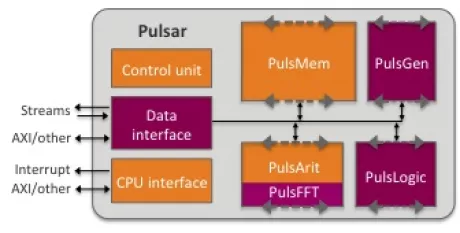

Scalable and Programmable Co-processor

- Hardware scalability to offer the best cost-performance trade-off

- Programmable Software-defined solution for flexible DSP components

- Enables complex DSP and high data-rate communication system design

- Can be optimized for FPGA and ASIC targets

-

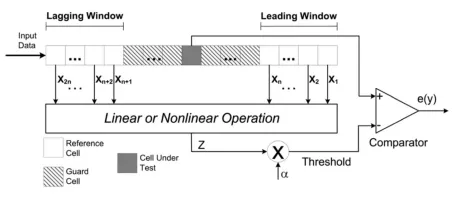

Constant False Alarm Rate Processor (CFAR)

- Removes a compute intensive task away from the microprocessor to a predictable, low-latency offload engine