Other

All offers in

Other

Filter

Compare

57

Other

from

27

vendors

(1

-

10)

-

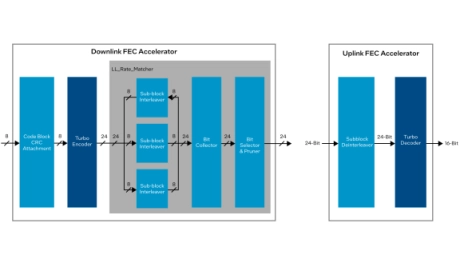

Turbo Intel® FPGA IP

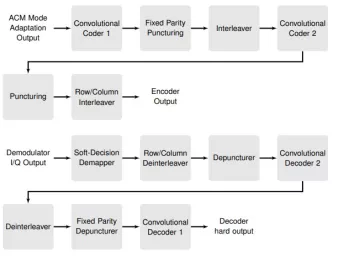

- Forward-error correction (FEC) channel codes commonly improve the energy efficiency of wireless communication systems

- Turbo codes are suitable for 3G and 4G mobile communications and satellite communications

- You can use Turbo codes in other applications that require reliable information transfer over bandwidth- or latency-constrained communication links in the presence of data-corrupting noise. The 4G Turbo-V Intel® FPGA IP comprises a downlink and uplink accelerator for vRAN and includes the Turbo Intel® FPGA IP.

-

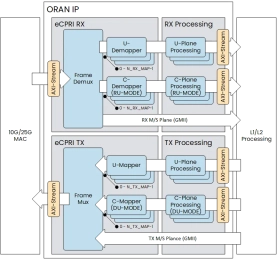

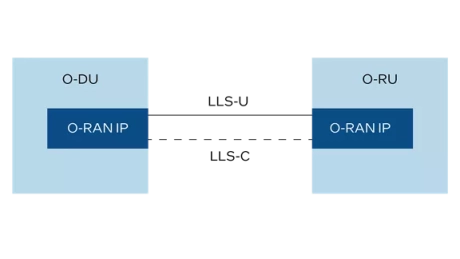

ORAN IP core

- ORAN IP core is a highly scalable and silicon agnostic implementation of the interoperable O-RAN WG4 defined 7.2x interface for deployment in O-DU and O-RU products, targeting any ASIC, FPGA or ASSP technologies.

- The ORAN over eCPRI implementation builds on long-time experience designing CPRI and Radio-Over-Ethernet solutions for fronthaul and delivers a flexible engine that is prepared for tight integration with software applications.

-

-

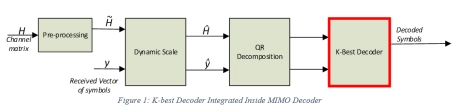

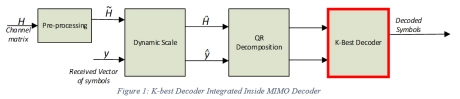

K-Best MIMO 3×3 Decoder

- Fixed Depth K-Best Decoder (K=16)

- Achieves close-to ML BER performance

- Supports three streams with different QAM (from BPSK to 64 QAM)

- Supports square and non-square QAM

- Supports OFDM based systems with different Space Time Coding (STC)

-

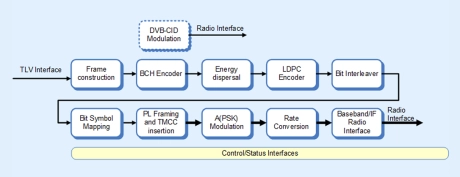

ISDB-S3 modulator

- The Commsonic CMS0070 ISDB-S3 Modulator with integrated LDPC encoder has been designed specifically to address the requirements of the ARIB STD-B44 advanced wide-band digital satellite standard.

- The core provides all the necessary processing steps to modulate a single transport stream (or baseband frame) into a complex I/Q signal for input to a pair of DACs, or an interpolating DAC device such as the AD9857(or AD9957). Optionally, the output can be selected as an IF to supply a signal DAC.

-

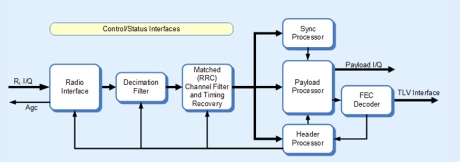

ISDB-S3 demodulator

- The CMS0071 ISDB-S3 Demodulator is a high-performance (A)PSK demodulator core intended for ARIB STD-B44 ISDB-S3 advanced wide band digital satellite standard.

- Operating symbol rate is programmed from a register and extends from approximately 40% of the master clock frequency down to an arbitrary low rate that is set through synthesis options. The range would normally be dictated by the application and, in particular, the phase noise characteristics of the radio system.

-

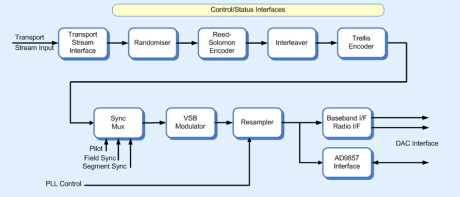

ATSC 8-VSB modulator

- The CMS0033 ATSC 8-VSB Modulator with integrated Channel Coder has been designed specifically to implement the 8-VSB requirements of the ATSC Digital Television Standard (A/53).

- The core provides all the necessary processing steps to modulate a single transport stream into a complex I/Q signal for input to a pair of DACs, or a DDS up-conversion DAC such as the AD9857(or AD9957). Optionally, the output can be selected as an IF to supply a signal DAC.

-

O-RAN Intel® FPGA IP

- The Extensible Radio Access Network (O-RAN WG4 Fronthaul Interface) defines a fronthaul interface between a lower-layer split distributed unit (DU) and remote unit (RU) in an Evolved Universal Terrestrial Access Network (E-UTRAN) and Next-Generation Radio Access Network (NG-RAN) system with a lower layer functional split-7-2x based architecture

- The O-RAN IP implements control and user plane protocol specified in O-RAN-FH.CUS.0-v03.00.

-

CCSDS SCCC Turbo Encoder and Decoder

- Burst-to-burst on-the-fly configuration

- High payload block length granularity (between 5,758 and 43,678 bits)

- High code rate granularity (code rates between 0.36 and 0.90)

- Configurable amount of turbo decoding iterations for trading off throughput and error correction performance

-