Peripheral Controller IP

Welcome to the ultimate Peripheral Controller IP hub! Explore our vast directory of Peripheral Controller IP

All offers in

Peripheral Controller IP

Filter

Compare

21

Peripheral Controller IP

from

12

vendors

(1

-

10)

-

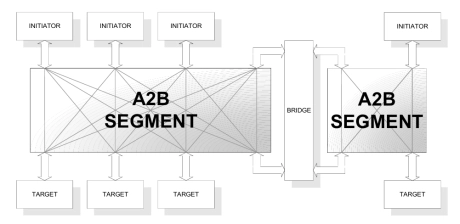

A2B System Interconnect

- A2B is a high performance System-on-Chip interconnect designed for use in synthesizable designs.

- It is specifically developed to meet the challenges of multiprocessor and multiple DMA / IO processor designs.

- A2B is designed to have the highest possible occupancy so that the sustainable bus bandwidth closely approaches the available peak bandwidth of a given configuration.

-

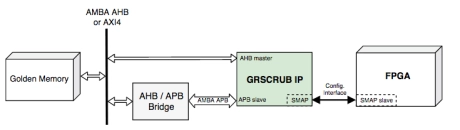

FPGA Scrubber Controller

- GRSCRUB is an FPGA supervisor responsible for programming and scrubbing the FPGA configuration memory to prevent the accumulation of radiation-induced errors.

- The GRSCRUB IP currently supports the AMD/Xilinx Kintex UltraScale and Virtex-5 FPGA families.

-

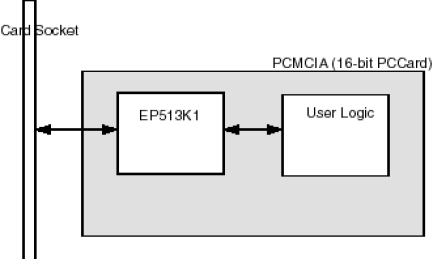

Compactflash/PCMCIA Slave Controller

- Functions as card interface on the card side.

- Support PCMCIA and CompactFlash devices.

- Operates asynchronously to the host devices in the other side of the card socket.

- Synchronous interface to user logic in the card side.

-

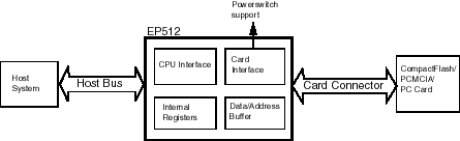

CompactFlash/PCMCIA Host Controller with EXCA Registers

- Compliant with PC Card Standard 8.0, PCMCIA 2.1/JIEDA 4.2 and CompactFlash 1.4.

- Allows host CPU to access CompactFlash, PC Card/PCMCIA devices.

- 82365SL-compatible register set, EXCA compatible.

-

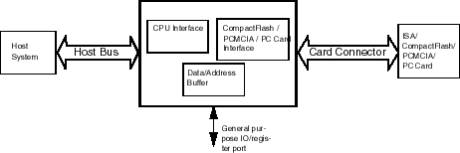

CompactFlash/PCMCIA Host Controller

- Compliant to ISA bus, CompactFlash specification and PC Card/PCMCIA standards.

- Allows host bus devices to access ISA bus, CompactFlash, PC Card/PCMCIA devices.

- Different user interface options to support various CPU?s including I960, X-86, PowerPC, MPC860, ARM, SH2/3/4 microprocessors.

- In PC Card/PCMCIA mode, supports attribute memory access, common memory access and IO access.

-

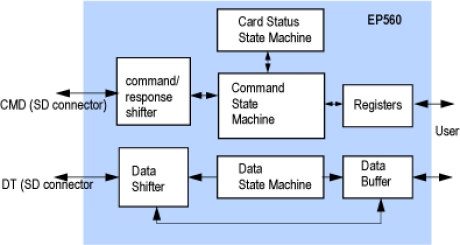

SDIO/SD Memory/MMC Slave Controller

- Compatible with SD/SDIO specification 2.0 with 1 and 4 bit data transfer.

- Provides SD interface to peripheral or memory device through a simple address/data interface.

- Support SD, SPI and optional MMC bus protocol.

- Support for both standard capacity and high capacity (SDHC) memory cards.

-

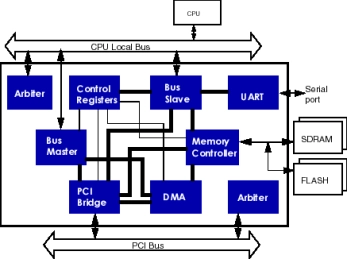

System Controller

- The system controller core connects the system CPU to system memory, PCI bus, IO ports and external communication links.

- While the CPU’s task in the system is to process data, the system controller’s main function is to coordinate data movement in the system.

- The system controller contains all the major functional modules required for most System-on-Chip (SOC) application.

-

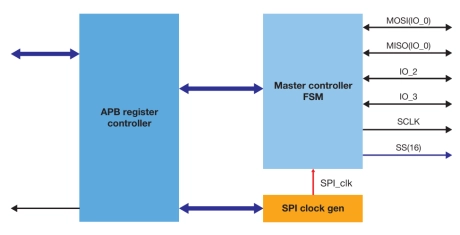

Quad SPI Controller

- Configurable SPI modes

- Supports programmable SPI clocking modes

- Programmable interrupt on SPI-done

-

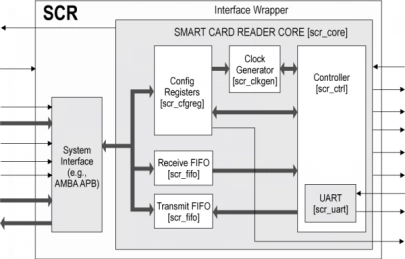

Smart Card Reader Controller

- Implements an interface and controller for communicating between smart cards and host systems using a variety of standard system interfaces.

- The SCR supports the ISO/IEC 7816-3:2006 and EMV 4.3 specifications, which define the electrical signals and transmission protocols for smart cards (also known as integrated circuit cards).

- It acts as a communication controller, passing data to and from the host system and the smart card.

-

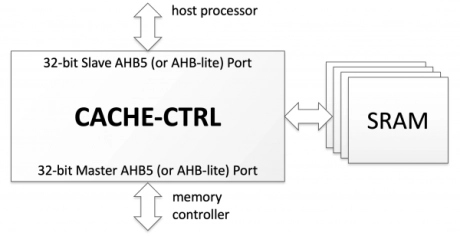

AHB Cache Controller

- The CACHE-CTRL IP core is a flexible cache memory controller providing a 32-bit slave processor interface and a 32-bit master interface to the memory subsystem. The processor and memory interfaces are natively AHB5 and can easily be reduced to AHB-lite.

- The cache controller core supports a four-way associative cache memory and implements a Least Recently Used (LRU) replacement policy.