Other

All offers in

Other

Filter

Compare

84

Other

from

32

vendors

(1

-

10)

-

-

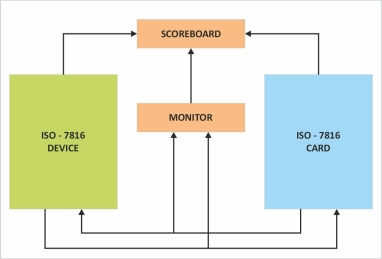

ISO/IEC 7816 Verification IP

- The ISO/IEC 7816 Verification IP offers a streamlined and efficient solution for verifying System-on-Chip (SoC) and IP designs that incorporate contactless communication.

- The ISO/IEC 7816 VIP is compliant with ISO/IEC 7816 Specifications. This VIP is light weight with easy plug-and- play interface so that there is no hit on the design cycle time.

-

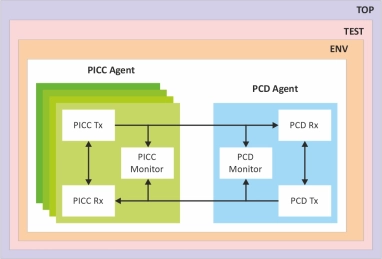

ISO/IEC 14443 Verification IP

- This VIP provides a comprehensive environment for verifying devices acting as either a Proximity Coupling Device (PCD) or a Proximity Integrated Circuit Card (PICC).

- Fully compliant with the complete ISO/IEC 14443 standard (Parts 1-4), our VIP is a lightweight, plug-and-play solution designed to ensure rigorous verification, minimize design cycle time, and accelerate your time-to-market.

-

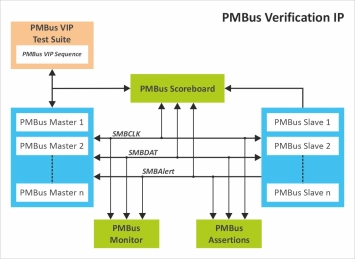

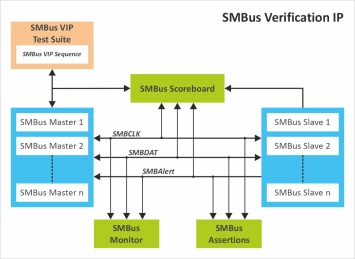

SMBus Verification IP

- Fully compliant with Rev. 3.3.1 of the SMBus Specification.

- Support PEC (Packet error Checking) for communication robustness.

- Support for all Bus protocols with and without PEC.

- Support for SMBus ARP (Address Resolution Protocol) for dynamically assigning a unique address to each slave device.

- Support for Clock Synchronization & Arbitration for Multi Master.

-

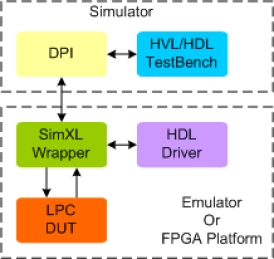

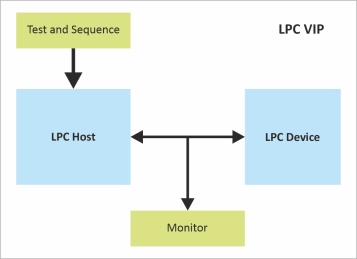

LPC Verification IP

- The LPC Verification IP provides an effective & efficient way to verify the LPC components of an IP or SoC.

- The LPC VIP is fully compliant with LPC Specification version 1.1

- The VIP is lightweight with easy plug-and-play components so that there is no hit on the design cycle time.

-

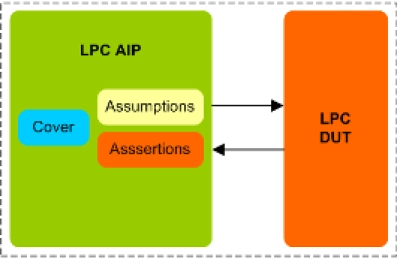

LPC Assertion IP

- Compliant to LPC 1.1 specifications.

- Supports bandwidth upto 33 MHz.

- Supports the following operations

-

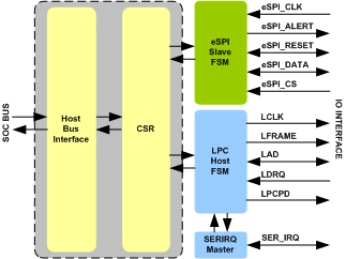

eSPI LPC Bridge IIP

- Compliant with version 1.1 LPC Interface Specifications and eSPI base specification as defined in Enhanced Serial Peripheral Interface (eSPI) Specification rev.1.0

- Converts eSPI Peripheral Channel Transactions into LPC Memory write or read instructions

- Supports full LPC host capability

- Supports SOC Slave

-

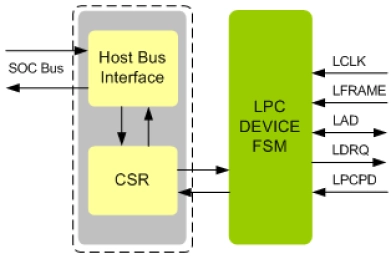

LPC Device IIP

- Compliant with version 1.1 LPC Specification.

- Full LPC Device/Peripheral functionality

- Supports the following operations:

- Memory read and write

-

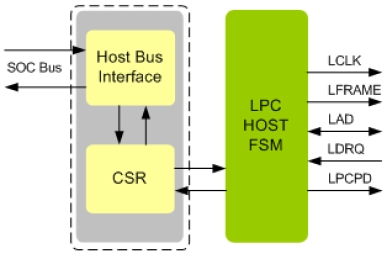

LPC Host IIP

- Compliant with version 1.1 LPC Specifications.

- Full LPC Host functionality.

- Supports the following operations:

- Memory read and write

-

LPC Synthesizable Transactor

- Compliant to LPC 1.1 specifications.

- Supports bandwidth up to 33 MHz.

- Supports the following operations

- Memory read and write