SATA IP

Welcome to the ultimate SATA IP hub! Explore our vast directory of SATA IP cores.

SATA-IP IP cores are designed to handle SATA Protocol and communicate with SATA compliant device without need CPU/OS and External DDR memory. SATA storage is suitable for low cost and large storage capacity with easily scalable SATA Channel to support RAID system.

All offers in

SATA IP

Filter

Compare

92

SATA IP

from

23

vendors

(1

-

10)

-

SATA-III Host Controller

- Fully compliant with the Serial ATA specification revision 2.6

- Simple transaction interface with Host processor and DMA Engine

- 32-bit internal data path

- 8KB FIFO implemented by BlockRAM in both transmit and receive paths

-

SATA-II Host Controller Core

- Fully compliant with the Serial ATA specification revision 2.6

- Simple transaction interface with Host processor and DMA Engine

- 32-bit internal data path

- 8KB FIFO implemented by BlockRAM in both transmit and receive paths

-

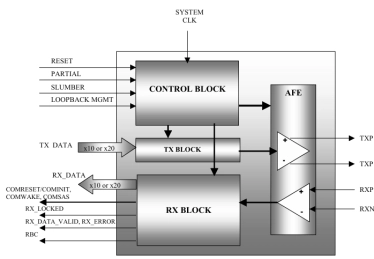

Serial ATA (SATA) PHY Transceiver IP

- SMS6000 is a fully integrated CMOS transceiver that handles the low level Serial ATA protocol and signaling.

- It contains all necessary Clock synthesis, Clock Recovery, Serializer, Deserializer, Comma detect for 8B/10B encoded data and Frame alignment functionalities.

-

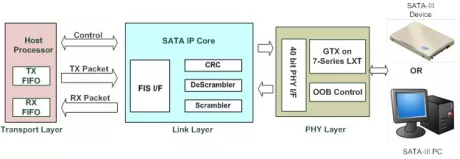

SATA-IP core - File system management without CPU

- SATA IP core compliant with the Serial ATA specification revision 3.0 and work on AMD UltraScale and 7-Series device.

- This IP core provide link layer. Design Gateway provide transport layer and 150MHz GTX physical layer design for 6.0Gbps SATA-III interface as reference design.

- It can connect with SATA-III HDD directly without external PHY chip.

-

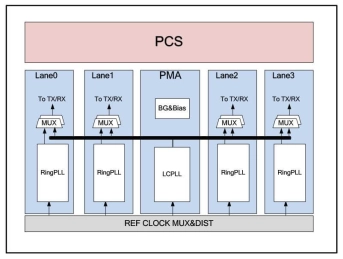

SATA/SAS 3.0 transceiver IP with PMA and PCS layer

- Highly customizable PMA configuration (controlled by PCS), X4 per Quad

- Support SATA data rate 1.5/3/6Gbps

- Support SAS data rate 1.5/3/6/12Gbps

- Digitally-control-impedance termination resistors

-

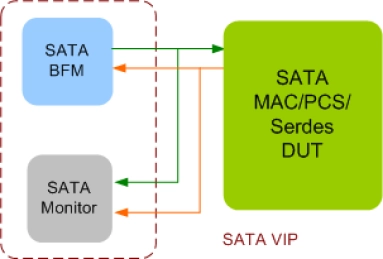

SATA Verification IP

- Supports SATA specs 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5.

- Supports 1.5, 3 and 6 Gbps speeds.

- Supports Port Multiplier Discovery and Enumeration.

- Supports following interfaces

-

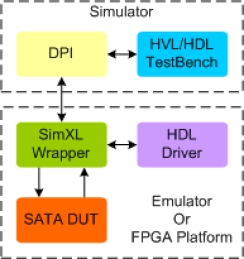

SATA Synthesizable Transactor

- Supports SATA specs 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5.

- Supports 1.5, 3 and 6 Gbps speeds.

- Supports Port Multiplier Discovery and Enumeration.

- Supports TBI interface with following bits

-

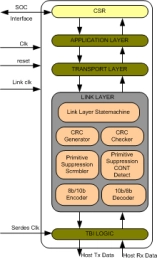

SATA HOST CONTROLLER IIP

- Supports SATA specs 2.5/2.6/3.0/3.1/3.2/3.3/3.4/3.5.

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

-

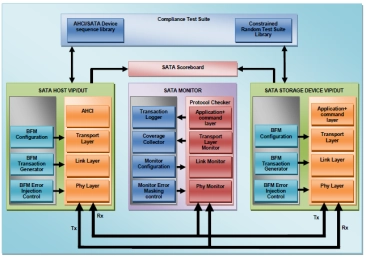

SATA 3.3 Verification IP

- Compliant to SATA 3.3, PIPE and AHCI 1.3.1 Specification and backward Compatible to SATA 1.0 ,SATA 2.0 and SATA 3.2 specification.

- Supports AHCI functionality on Host (HBA) side.

- Supports complete functionality of Application, Command, Transport, Link and PHY Layer.

- Configurable PIPE Interface width 8,16 or 32 bits.

-

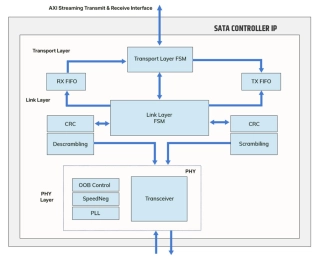

SATA 3 Controller IP

- Simple AXI streaming TX and RX interface for application layer communication.

- It supports Native Command Queuing and key primitives/FIS types from SATA specifications.

- Compliant with Serial ATA 3.0 specification.

- Supports data rates of 1.5/3/6 Gbit/s.