Towards Self-Driving Cars: MIPI D-PHY Enabling Advanced Automotive Applications

By Mahmoud Banna, Julian Schiralli (Mixel)

Since the invention of the automobile well over a century ago, car manufacturers have been focused on creating the highest-speed, safest, and most fuel-efficient cars possible. As standards for each of those metrics have reached a peak, manufacturers have incorporated other avenues of differentiation with an eye toward technology, implementing cameras and sensors to create features that would have been science fiction only 20 years ago. These technologies are turning cars from something that simply gets a driver from point A to point B manually, to an experience that is evolving to require less and less human control, slowly turning the driver into a passenger.

Cameras and sensors are not new to the automotive industry; dashboard and backup cameras have become ubiquitous in the past 10 years. What is new; however, is the use of onboard cameras and sensors for Advanced Driver-Assisted Systems (ADAS), the first step in the industry’s inevitable progression toward Autonomous Driving Systems (ADS). These cameras and sensors work together to do things like eliminate blind spots, provide warnings in case of lane departure, and keep consistent distance between cars, reducing mortality in accidents and making cars safer overall. In order to make this happen, behind the scenes, an enormous amount of data from each of the cameras and sensors needs to be processed at blazing speed. This requires unique SOC solutions to the automotive application’s specific challenges.

For ADAS to work smoothly, the incorporated camera and sensor SOC designs must support high bandwidth to accommodate higher sensor resolution, lower system latency, high dynamic range and display resolution requirements. Meeting those requirements has to be balanced with the need for low power and the ability to pass stringent safety testing. Keeping up with the data requirements needed for ADAS has resulted in substantial growth in the adoption of interfaces and specifications supporting automotive sensors and displays over the past several years. While there are several different interfaces that can meet the speed requirements, MIPI® specifications provide the best balance between the high-speed, low-latency and low power dissipation requirements. This is because MIPI specifications are crafted to meet the stringent requirements of mobile and mobile-influenced applications. Let’s take a closer look at several key (or “the predominant”) MIPI specifications in ADAS today and how they enhance this burgeoning technology.

MIPI in ADAS

Because both viewing and sensing ADAS applications must handle imaging, sensing, high-speed serial communication, and downstream processing functions, Camera Video Processors (CVPs) are always located at the heart of these systems. As more cameras and sensors are added to the system to aid in increasingly complicated tasks, more integrated CVP solutions are required. Ideally, these CVPs should process data received from multiple high dynamic range sensors and drive high-resolution displays, automotive SerDes links, and computer vision processors with minimal power consumption and low latency. This is where the MIPI specifications come into play.

High-bandwidth performance, scalability, low latency, low power and low EMI are the fundamental features of MIPI physical layer and protocol specifications. These unique attributes are perfect match for automotive applications, making the MIPI D-PHYSM a prerequisite for all ADAS applications. MIPI D-PHY is a simple source synchronous PHY that uses one clock lane and a varying number of data lanes. It has been around since 2009, and widely deployed in MIPI CSI-2SM and DSISM (and later, DSI-2SM) applications. The single-lane D-PHY v1.2 configuration requires four pins, two pins for clock lane and two pins for data lane, achieving data rate up to 2.5 Gbps.

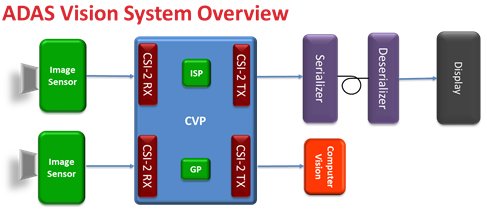

Figure 1 below gives an overview of ADAS vision system and shows the role of MIPI interfaces in such system.

Figure 1: MIPI in ADAS Vision System

As you can see in figure 1, the CSI-2 interface is commonly used in ADAS applications as the communication link between the sensors on one side and a CVP on the other. The CVP drives the processed video through a MIPI CSI-2 TX interface to an automotive SerDes link, which might be driving a high-resolution display through MIPI D-PHY based DSI interface. For the computer vision applications, the unprocessed high-resolution video is transmitted from a CVP to a computer vision processor through another pair of MIPI CSI-2 TX/RX interfaces. Both DSI and CSI-2 are MIPI protocols that send data over MIPI D-PHY physical layer.

Now, let’s take a look at how Mixel’s MIPI D-PHY IP plays a key role enabling advances in ADAS applications.

Mixel’s MIPI D-PHY IP

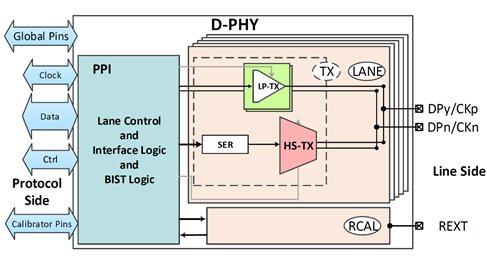

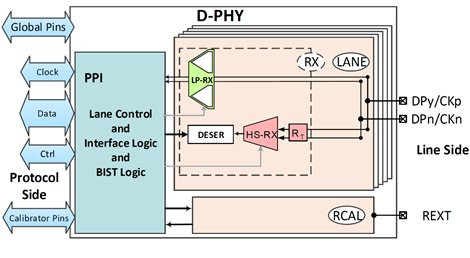

Mixel’s MIPI D-PHY TX and RX IPs are optimized for transmit and receive functionality to reduce area overhead. Each support up to 4 lanes, with D-PHY v1.2 running at 2.5 Gbps per lane.

For the D-PHY TX, a CSI-2 TX controller is used with a total bandwidth up to 10 Gbps across all lanes and includes support for virtual channels. The Mixel D-PHY RX is similar in bandwidth and uses a CSI-2 RX controller. As this is an automotive application, both the D-PHY TX and RX are AEC-Q100 compliant for auto-grade 0/1/2 temperature ranges.

Figure 2: Mixel MIPI D-PHY TX Block Diagram

Figure 3: Mixel MIPI D-PHY RX Block Diagram

Each PHY is also equipped with built-in-self-test (BIST) engine that enables testing of the PHY across several layers of abstraction (IC, PCB, System). The BIST engine can test the PHY in different MIPI modes of operation with improved observability and controllability. A variety of test scenarios have been implemented to enable both production and characterization testing.

Mixel MIPI D-PHY IPs have been silicon-proven in multiple process nodes and foundries, and widely deployed in automotive applications chipsets.

GEO’s Use-Case

GEO, a market leader in providing CVP based solutions for automotive viewing cameras, integrated Mixel D-PHY v1.1 RX and TX solutions in their recently announced GW5 CVP product family for next generation automotive cameras and achieved first-time silicon success. Mixel D-PHY v1.1 supports 1.5 Gbps data rate per lane, achieving 6 Gbps aggregate bandwidth using four data lanes.

GEO’s GW5 CVP product family represents the world’s first edge based automotive smart viewing camera processors. The GW5200 is the cutting edge in automotive camera video quality, while the GW5400 adds in-camera computer vision to enable ADAS functionality and facilitate applications like pedestrian, object, and blind-spot detection, as well as cross traffic alerts, driver attentiveness, and auto calibration of the smart camera.

The GEO GW5 supports up to 8-megapixels of resolution and includes GEO’s proprietary 5th-generation eWARP® geometric processor, innovative High Dynamic Range (HDR) Image Signal processor (ISP), and 2D graphics functionality. The ISP supports the most advanced HDR, and LED Flicker Mitigation. It also allows for on-chip merging of up to four exposures, which drives the dynamic range up to 140dB. The 2D Vector Graphics Engine renders high-resolution real-time graphics to overlay on the video stream, enabling compelling user interfaces. The GW5 CVP has been developed to meet ISO 26262 ASIL-B and is AEC-Q100 Grade 2 qualified.

Both D-PHY RX and TX interfaces are required as main video interfaces for the GW5 family. For D-PHY RX, all automotive sensors are MIPI CSI-2 D-PHY v1.1 or 1.2 oriented. In the GW5 CVP use case, two D-PHY RX interfaces were required for dual sensor support. If more than two sensors are required, MIPI virtual channels can be used to enable processing multiple independent sensors per single MIPI D-PHY RX interface, allowing the GW5 to support applications like surround view monitors. Each MIPI RX interface is also capable of receiving multiple exposures sent from HDR sensors and recombining them into a single high-dynamic range video from.

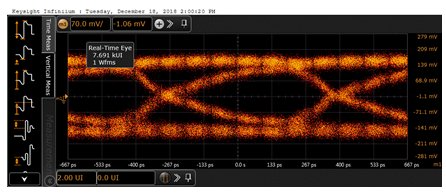

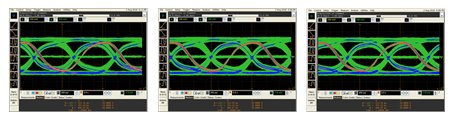

For D-PHY TX, two interfaces were deployed to provide high bandwidth video downstream. The two interfaces can be used to send processed video for display and unprocessed high-resolution video for computer vision. Using MIPI virtual channels, each interface can send multiple video channels on the same MIPI port. This feature can be used in case of dual sensor input, where the two video streams can be individually processed and sent over the same MIPI TX interface through virtual channels. Below are two snapshots of the test results of Mixel D-PHY TX and RX in the GEO GW5.

Figure 4: Mixel MIPI D-PHY TX Eye Diagram at 1.5Gsps

Figure 5: Mixel MIPI D-PHY RX setup/hold margins test at 1.5Gbps

Driving into the Future

The evolution of ADAS applications along with the increased adoption of the numerous driver assistance features continue to enhance the overall driving experience, safety, comfort and convenience, and give rise to the highest level of automation represented in fully Autonomous Vehicles (AVs).

With ADS, the vehicle should be capable of performing all driving functions under all conditions. To achieve this, the vehicle will not only communicate with its internal complex systems, but much more communication will take place with the external environment. The future automotive technologies will continue to use an ever-increasing number of cameras, radar and lidar sensors. The sensor technologies will have to be more robust and capable of handling more complex tasks. The automotive system components should provide higher performance in order to handle more data communication, with higher speed, and minimal latency and power consumption.

The MIPI CSI-2/DSI protocols along with higher bandwidth D-PHY will continue their progression toward supporting higher performance automotive sensors and systems. With Mixel’s many MIPI PHY optimized configurations, unique patented testability features, widest coverage of foundries and process nodes and support for ever increasing data rates, Mixel is well poised to continue to play a central role in supporting the MIPI ecosystem, particularly in the ever evolving and exponentially growing automotive market.

References:

For information about Mixel’s IP portfolio, visit mixel.com/ip-cores.

For more about Mixel’s IP at Design & Reuse:

- Mixel’s MIPI D-PHY TSMC 28HPC+ CSI-2 RX

- Mixel’s MIPI D-PHY TSMC 28HPC+ CSI-2 TX

- Mixel’s MIPI D-PHY TSMC 16FFC Universal for Automotive

About the Authors

Mahmoud Banna

ASIC Manager, Mixel, Inc.

Mahmoud Banna has been working since 2011 for Mixel, where he heads the ASIC team in Egypt. Prior to that position, he led a team working on serial link products such as USB and PCI Express. Banna has 12 years of ASIC design and management experience. He holds a BSEE from Ain Shams University and MBA from the American University in Cairo.

Julian Schiralli

Principal ASIC Designer, GEO Semiconductor

Julian Schiralli is a Principal ASIC Designer at GEO Semiconductor, with over two decades of professional experience in the Video field. Julian has been witness to the flat panel LCD revolution in both television and computer monitor, having served roles of team member and manager with such companies as Genesis Microchip and ST-MicroElectronics. In recent years Julian has focused his attention on the automotive sector, and the challenges therein. A strong believer of lead by example in the workplace, Julian regularly collaborates with peers to deploy winning strategies for chip design.

Related Semiconductor IP

- MIPI SoundWire I3S Peripheral IP

- MIPI SoundWire I3S Manager IP

- MIPI SWI3S Manager Core IP

- MIPI I3C Target Device

- MIPI CSI-2 IP

Related Articles

- Analog switches in D-PHY MIPI dual camera/dual display applications (Part 1 of 2)

- Analog switches in D-PHY MIPI dual camera/dual display applications (Part 2 of 2)

- e Verification Environment for FlexRay Advanced Automotive Networks

- Building advanced Cortex-M3 applications

Latest Articles

- Extending and Accelerating Inner Product Masking with Fault Detection via Instruction Set Extension

- ioPUF+: A PUF Based on I/O Pull-Up/Down Resistors for Secret Key Generation in IoT Nodes

- In-Situ Encryption of Single-Transistor Nonvolatile Memories without Density Loss

- David vs. Goliath: Can Small Models Win Big with Agentic AI in Hardware Design?

- RoMe: Row Granularity Access Memory System for Large Language Models