Validating UPLI Protocol Across Topologies with Cadence UALink VIP

The UPLI (UALink Protocol Level Interface) is a logical signaling interface that facilitates communication between devices—specifically between originator devices (which initiate transactions) and completer devices (which respond to them). Each transaction comprises a request and a corresponding response, forming a complete communication cycle. Cadence UALink VIP supports various topologies to verify UPLI layer of DUT.

1. Standalone UPLI topology enables users to verify UPLI originators and/or UPLI completers independently and would help user verify protocol layer functionality, bypassing lower layers and saving sim cycles.

Cadence UALink VIP has three flavors to verify the standalone UPLI layer as shown below.

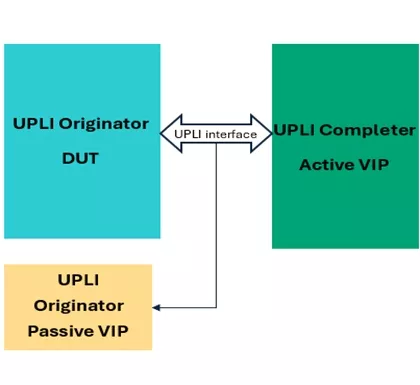

- DUT originator and VIP completer: In this topology the DUT is responsible for initiating transactions by issuing request messages such as reads, writes, or atomic operations. The verification focuses on ensuring the DUT correctly forms these requests, manages transaction tags for multiple outstanding transactions, and properly processes the corresponding responses returned by the VIP. The VIP acts as a target device that can respond to requests. Passive originator VIP agent receives and validates the format and legality of the Requests from the DUT. As a completer, the VIP must generate and transmit a valid response for every request it receives, as all requests require a response. The VIP can be configured to control responses and their timing to test the DUT's ability to handle many outstanding transactions.

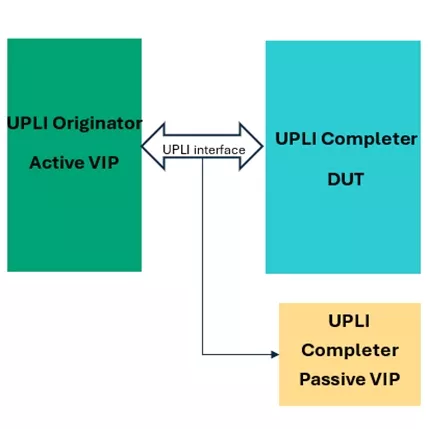

- VIP originator and DUT completer: The VIP generates a wide range of legal requests (commands) and sends them to the DUT. The VIP can create complex scenarios with multiple outstanding transactions using different transaction tags to stress the DUT's processing capabilities. After issuing requests, the passive VIP agent monitors and validates the responses from the DUT. The DUT must be able to receive and process incoming requests from the VIP. Verification focuses on the DUT's ability to correctly parse different command types, perform the requested memory operations, and generate and send back a valid, properly tagged Response for each transaction.

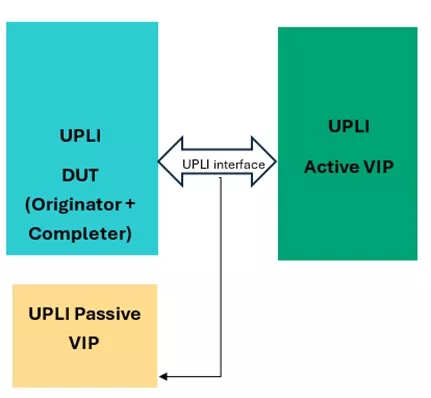

- DUT and VIP both has originator + completer pair (combined agent): This setup verifies the DUT's ability to manage simultaneous, bidirectional traffic. The DUT's originator initiates transactions that are received by the VIP's completer, while the DUT's completer receives and processes transactions initiated by the VIP's originator. This configuration can emulate the complex request and response paths found in a switched environment. For example, a request from the DUT's originator might be received by the VIP's completer, which then emulates a switch by re-issuing a new request from its originator back to the DUT's completer. This verifies the DUT's ability to handle the symmetrical, but opposite-direction flows of requests and responses that occur in multi-device UALink pods.

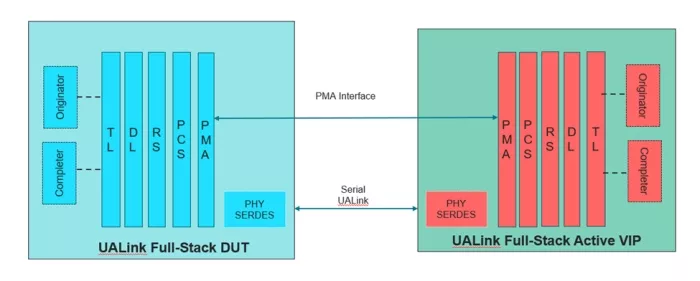

2. Full stack DUT with UPLI: This full-stack topology enables users to verify the entire UALink protocol stack, from the UPLI layer down to the physical layer, in a realistic and integrated environment. It ensures that end-to-end data integrity is maintained across the complete communication path, which is critical for validating correctness in real-world scenarios. By including both the originator and completer roles on both DUT and VIP sides, this setup allows for bi-directional traffic, simulating actual system behavior. Additionally, it helps verify real-time path delays, buffering behavior, and flow control across intermediate layers such as the transport, data link, and physical layers. These intermediate layers play a crucial role in flit conversion, CRC/FEC handling, and serialization, all of which must be validated to ensure protocol compliance and performance.

- For more info on Cadence UALink Verification IP, please visit our product page Simulation VIP for UALink.

- To know more about UALink specification and its updates, please visit the UALink consortium website.

Explore UALink VIP IP:

Related Semiconductor IP

- Simulation VIP for UALink

- UALink Controller

- UALink PCS IP Core

- Verification IP for UALink

- UALink IP Solution

Related Blogs

- VIP Portfolio Expands for Data-Intensive Hyperscale Data Centers, HPC, and AI/ML

- Industry's First Adopted VIP for PCIe 7.0

- Audio Transport in DisplayPort VIP

- UALink: Powering the Future of AI Compute

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk