Streamlining SoC Integration With the Power of Automation

By Insaf Meliane, Product Management & Marketing Manager at Arteris

The rapid acceleration of semiconductor technologies is creating system-on-chip (SoC) devices that are increasingly complex. These chips contain billions of transistors and hundreds of functional intellectual property (IP) blocks. This exploding complexity requires the automation of the SoC integration, which is the process of instantiating, connecting and configuring all the IPs. This process often includes a mix of IPs from trusted third-party vendors and internally developed components distinguishing the design from competitors.

Third-party IPs commonly cover areas including communication functions, like Ethernet, USB and MIPI, as well as central processing units, graphics processing units, memory subsystems, and dynamic memory access controllers. Internally developed IPs may include hardware accelerators and machine learning inference engines. These IP blocks are heterogeneous with different formats, different protocols and different interfaces, and need to be integrated into one SoC that functions well. This integration process presents a multifaceted challenge in semiconductor design, going beyond what could be considered a simple plug-and-play approach.

Managing SoC integration is a demanding task, marked by inherent complexity and the potential for errors with data aggregation from different input formats and sources. Designers must collaborate across multiple teams, often distributed across various sites, leading to fragmented workflows. Many of their tasks require a significant amount of manual operations. These manual processes in SoC design can be error-prone and time-consuming, leading to delays in achieving time-to-market goals. These challenges highlight the need for a standardized approach to streamline and shorten the SoC integration.

Metadata in SoC Integration

Metadata, encompassing details about each IP, assumes a central role in the integration process. It provides essential information, which simplifies tracking and working with specific data. Traditionally, this information was meticulously handled manually and documented in data sheets or spreadsheets. Individual teams took responsibility for creating and maintaining these files, which often resulted in discrepancies when design choices weren't effectively communicated between the relevant teams.

IP-XACT for Standardization

In response to these challenges, the IP-XACT standard was developed as a universal format to exchange and reuse information about IPs and subsystems with a higher-level abstraction compared to traditional HDL languages. IP-XACT uses a machine-readable format (XML), enabling efficient automation and facilitating interoperability between the design flow steps with a proven correct-by-construction methodology, ensuring a high system quality. It includes built-in Semantic Consistency plus rules for better quality design with early issue detection. It also allows internal team cooperation, ensuring data consistency. To make the most of the standard, the right tools and a suitable development environment are necessary.

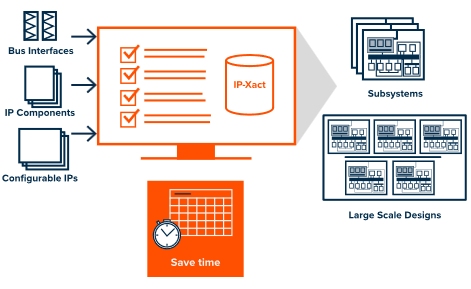

Reduce the Integration Process From Months to Weeks with Magillem from Arteris.

(Source: Arteris, Inc.)

Transforming SoC Integration

The Magillem tools from Arteris are a powerful solution for SoC integration automation based on the IP-XACT standard. It does more than just connect ports; it configures and instantiates each IP, recognizes each bus protocol, allowing the right bus interconnection. This results in a structured top-level RTL netlist, makefile scripts for EDA tools and connectivity reports that make integration more transparent. This environment makes it easy to make hierarchy adjustments, upgrade IPs, and restructure the design enabling design teams to be more flexible in adapting to constantly changing requests.

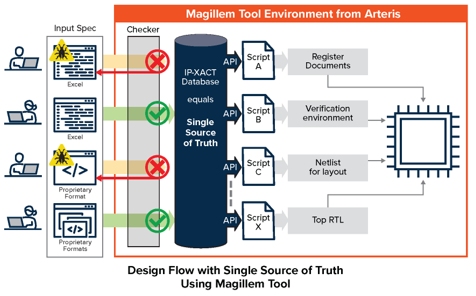

The Magillem tools serve as a single source of truth, ensuring synchronization between design teams that can all collaborate effectively to accelerate SoC development while mitigating design errors. It simplifies critical tasks such as building system memory map, generating error-free RTL register banks and creating thorough documentation.

Magillem Tools Enhance SoC Efficiency

By incorporating automation into a continuous integration pipeline and establishing a robust automated flow for the front-end design, Arteris uses its expertise to empower design teams, improve productivity, and ensure first-time-right projects. The company offers a trio of powerful products that redefine automation in SoC integration:

Magillem Connectivity accelerates the design of complex systems, simplifies the integration of IP blocks ensures superior quality and shortens design cycle times.

Magillem Registers autonomously constructs error-free system memory maps, ensuring the accuracy and reliability of SoC devices.

CSRCompiler streamlines the creation of hardware-software interfaces, giving the entire team a complete, correct, up-to-date register design ecosystem.

These products revolutionize the design process, rendering it more efficient, agile, and accurate. Design teams can harness these tools to maximize their productivity and expertise, delivering cutting-edge SoC devices with unparalleled efficiency.

(Source: Arteris, Inc.)

Conclusion

In SoC integration, automation is no longer a choice but a necessity. Automation tools and standards like IP-XACT are the linchpins propelling companies to the forefront of the market.

IP-XACT and tools like Magillem from Arteris offer an effective solution. By leveraging standardized metadata and an automation-friendly environment, design teams can streamline their processes, reduce design risks, and accelerate time-to-market. The Magillem tools from Arteris provide a path to successful SoC integration, ultimately improving the productivity of the team and the overall effectiveness of the SoC design.

For further information about SoC integration automation from Arteris, please click here.

Related Semiconductor IP

- Ultra-Low-Power LPDDR3/LPDDR2/DDR3L Combo Subsystem

- 1G BASE-T Ethernet Verification IP

- Network-on-Chip (NoC)

- Microsecond Channel (MSC/MSC-Plus) Controller

- 12-bit, 400 MSPS SAR ADC - TSMC 12nm FFC

Related Articles

- Revolutionizing Consumer Electronics with the power of AI Integration

- Creating SoC Designs Better and Faster With Integration Automation

- Unlocking the Power of Digital Twins in ASICs with Adaptable eFPGA Hardware

- Creating SoC Integration Tests with Portable Stimulus and UVM Register Models

Latest Articles

- Extending and Accelerating Inner Product Masking with Fault Detection via Instruction Set Extension

- ioPUF+: A PUF Based on I/O Pull-Up/Down Resistors for Secret Key Generation in IoT Nodes

- In-Situ Encryption of Single-Transistor Nonvolatile Memories without Density Loss

- David vs. Goliath: Can Small Models Win Big with Agentic AI in Hardware Design?

- RoMe: Row Granularity Access Memory System for Large Language Models