Unlocking the Power of Digital Twins in ASICs with Adaptable eFPGA Hardware

Adaptability is essential for digital twin systems due to constantly evolving environments – Learn how eFPGA hardware enables robust and adaptable systems

By Menta

What are digital twin systems and why are they so important?

Digital twin systems are crucial for industrial applications because they create real-time, data-driven virtual models of physical assets, processes, or systems. This enables companies to optimize performance, predict and prevent failures through predictive maintenance, and simulate design changes without the need for costly physical prototypes. By providing continuous monitoring and analytics, digital twins improve decision-making, enhance operational efficiency, and increase system resilience. They also support safety and regulatory compliance by allowing engineers to model hazardous scenarios and validate responses virtually. Ultimately, digital twins empower industries such as manufacturing, energy, automotive, aerospace, and industrial automation to operate more intelligently, efficiently, and safely.

| Benefits of Digital Twin Systems | Description |

| Operational Optimization | Continuously monitor and improve performance by identifying inefficiencies in real time |

| Predictive Maintenance | Forecast equipment failures and schedule maintenance before breakdowns, reducing downtime |

| Faster Innovation | Simulate design changes and system configurations virtually, reducing the need for physical prototypes |

| Improved Decision-Making | Use real-time analytics and modeling to make smarter operational and strategic decisions |

| Enhanced Safety & Compliance | Model hazardous scenarios and validate safety responses to meet regulatory standards |

| Greater Resilience | Increase agility and system resilience through real-time visibility and predictive insights |

Why is adaptability important for digital twin systems?

Adaptability is essential for digital twin systems in applications because these environments are constantly evolving—with ongoing changes in equipment, processes, workloads, and operating conditions. An adaptable digital twin can adjust to these changes in real time, supporting dynamic operations without the need for complete system overhauls.

This is especially important for ASICs and SoCs, which are typically fixed-function and deployed in systems with long lifecycles. As requirements shift over time, adaptable digital twins ensure these chips remain relevant by modeling new behaviors, configurations, or standards without requiring hardware redesign. When paired with adaptable hardware elements like embedded FPGA (eFPGA), digital twins can even guide runtime reconfiguration to optimize performance, enable new features, or respond to faults. They also enhance predictive maintenance by evolving with real-world data to identify emerging failure modes. During development, they accelerate validation and debugging by simulating a wide range of scenarios. And by enabling the simulation of new use cases and technologies, adaptable digital twins support ongoing innovation—making systems more resilient, future-proof, and capable of meeting the demands of modern industrial applications.

| Benefits of Adaptability | Description |

| Support for Evolving Requirements | ASICs often need updates to support new protocols, features, or algorithms over time |

| Real-Time System Tuning | Adaptable digital twins allow for in-system adjustments and optimization of ASIC behavior post-deployment |

| Predictive Maintenance Flexibility | ASICs embedded in machinery may face new failure modes—adaptable twins can evolve to detect them |

| Scalable Across ASIC Variants | As product lines evolve, digital twins must adapt to different ASIC configurations and use cases |

| Improved Simulation Accuracy | Ongoing adaptability ensures that digital twins reflect real-world ASIC performance with high fidelity |

| Faster Design Iteration | Engineers can test changes to ASIC logic or firmware in the twin before committing to physical changes |

| Support for Crypto Agility | In security-critical applications, adaptable twins help evaluate and manage algorithm changes dynamically |

| Lifecycle Extension | ASICs in industrial environments have long lifespans—adaptable twins help them stay relevant and effective |

Adaptable hardware is a valuable component in digital twins enabling flexibility, continuous adaptation while optimizing performance, and improving decision-making.

Adaptability in software or hardware?

In most of today’s ASICs, digital twin systems are implemented in software. However, implementing a digital twin purely in software for ASICs has benefits in simulation and modeling, but it falls short in several key areas that are critical for real-time, long-lifecycle, and high-reliability industrial applications. Here’s why software-only implementations are often insufficient:

| Limitation of Software Digital Twin Implementations | Explanation |

| Lack of Real-Time Responsiveness | Software models may not keep pace with the ultra-low-latency demands of real-time industrial ASIC operations |

| No In-System Adaptability | Software models may not keep pace with the ultra-low-latency demands of real-time industrial ASIC operations |

| Limited Visibility into Hardware States | Software cannot always capture internal states or signal-level behaviors within an ASIC, especially for security or timing-critical functions |

| Ineffective for On-Chip Fault Injection or Testing | Software can’t execute on-chip diagnostics or emulate real failure conditions at the hardware level |

| Higher Security Risks | Software layers can be more vulnerable to attacks than hardware-level monitoring and adaptability |

| Disconnect from Physical Behavior | Software simulations often lack fidelity in replicating noise, aging, thermal drift, or analog phenomena |

| Inability to Enable Hardware Adaptation | Software twins can’t change or reconfigure the hardware itself—needed for crypto agility, patching, etc |

In short, while software digital twins are useful for design-phase modeling and off-system analytics, they lack the real-time control, hardware visibility, and adaptability required to support long-term, mission-critical ASIC deployments. Hybrid approaches that integrate hardware-adaptable elements, like eFPGA, enable much more powerful, in-system digital twin capabilities.

Why Adaptable Hardware for Twin Systems?

Implementing digital twin systems with adaptable hardware (eFPGA) in ASICs delivers a range of critical advantages that traditional software or fixed hardware solutions cannot match. eFPGA enables in-system reconfigurability, allowing the digital twin to evolve alongside the physical asset over time. It provides real-time monitoring and control with ultra-low latency, making it ideal for precision industrial operations. eFPGA also supports predictive maintenance by enabling real-time diagnostics and adaptive fault detection. For security-sensitive applications, it facilitates crypto agility by allowing post-silicon updates to cryptographic algorithms. Additionally, eFPGA enables hardware-accelerated simulation, supports new protocols or features without ASIC respins, and tightly integrates with control systems to enhance responsiveness. These capabilities collectively extend the lifecycle of industrial ASICs, reduce cost and risk, and ensure the digital twin remains relevant and resilient in dynamic, mission-critical environments.

Applications of adaptable Digital Twin Systems

Next, let’s explore a few real-world applications of adaptable digital twin systems for industrial applications.

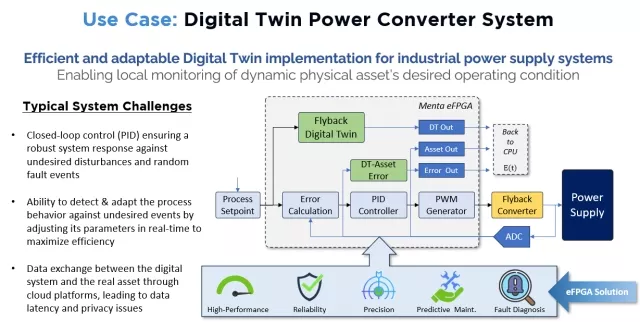

First let’s examine a Power Converter System:

In industrial power converter system ASICs, eFPGA allows the digital twin to accurately mirror and adapt to real-time electrical behavior with high fidelity, enabling optimal power conversion efficiency—a key metric that significantly enhances the value of power converters to customers. Power converters operate under rapidly changing load, temperature, and voltage conditions, and eFPGA allows the digital twin to monitor these parameters directly on-chip and dynamically adjust control logic, protection schemes, or modulation algorithms. This adaptability is crucial for predictive maintenance, fault detection, and optimizing power efficiency over time. As power electronics standards and safety regulations evolve, eFPGA also allows the digital twin logic to be reconfigured post-silicon—extending the ASIC’s usable life without a costly redesign. Additionally, eFPGA-based twins can simulate stress scenarios in-system (e.g., overvoltage, thermal drift, aging), enabling smarter real-time diagnostics and safer operation. This makes eFPGA an essential enabler for resilient, adaptive, and future-ready digital twin systems in industrial power converter ASICs.

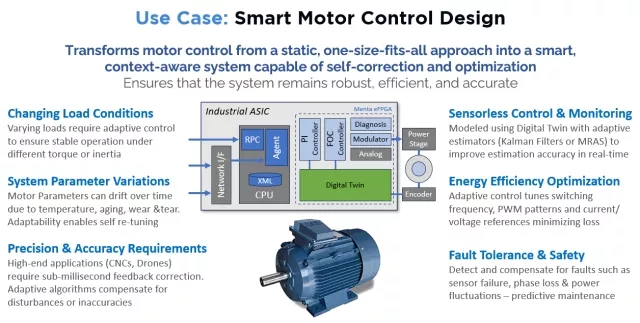

Next, lets consider a Smart Motor Control Design

In industrial motor control systems, eFPGA enhances digital twin functionality by enabling on-chip, real-time adaptation to changing load conditions, speed profiles, and environmental factors. Motor control ASICs often require ultra-low-latency feedback loops for torque control, position sensing, and current regulation—functions that eFPGA can dynamically fine-tune as conditions evolve. This adaptability supports predictive maintenance by detecting anomalies such as bearing wear or imbalance early, allowing the digital twin to simulate and respond to degradation before failure occurs. eFPGA also provides the flexibility to update control algorithms post-deployment, enabling support for different motor types or evolving industrial protocols without a hardware respin. Additionally, it allows in-system testing and fault injection to validate safety-critical control routines in real-world conditions. Together, these capabilities make eFPGA a key enabler for robust, efficient, and future-proof motor control systems in industrial applications.

And consider that Industrial systems may use different motor types (BLDC, PMSM, induction), and control algorithms often need to be tailored or updated. eFPGA allows post-silicon reconfiguration to adapt the ASIC to various motor types without redesign.

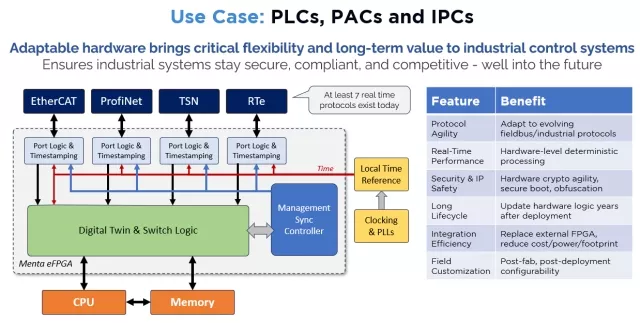

And finally, let’s look at Industrial Automation Controllers – PLCs, PACs and IPCs.

In industrial controllers like PLCs, PACs, and IPCs, eFPGA enhances digital twin systems by enabling real-time adaptation of logic functions, signal processing, and interface handling—directly in hardware. These controllers often operate in diverse and evolving environments, requiring frequent updates to control algorithms, industrial protocols, or I/O configurations. With eFPGA, the digital twin can adapt in-system without needing to change the silicon, enabling rapid deployment of updates or support for new machine configurations. This is especially valuable for predictive maintenance and diagnostics, where real-time hardware monitoring and on-the-fly logic adjustments can prevent downtime. eFPGA also supports secure, hardware-based responses to system faults or cybersecurity threats, extending the controller’s resilience. Furthermore, as industrial standards and connectivity requirements evolve, eFPGA allows the digital twin to remain aligned with operational demands, reducing the need for costly hardware replacements. This makes eFPGA a strategic asset in building agile, future-ready industrial automation platforms.

While these three examples highlight real-world applications of adaptable digital twin systems, they represent just a fraction of their potential. Here’s how adaptable digital twins deliver value across a wide range of industries:

| Industry | Use Case |

| Manufacturing | Process optimization, predictive maintenance, quality control, and production line simulation |

| Aerospace & Defense | Mission readiness, system diagnostics, lifecycle management of aircraft and defense systems |

| Energy & Utilities | Grid management, power plant monitoring, turbine diagnostics, and predictive failure prevention |

| Automotive | Vehicle design, testing, and performance simulation; connected car monitoring and updates |

| Industrial Automation | Enhancing PLCs, PACs, and IPCs for adaptive control and real-time system modeling |

| Oil & Gas | Monitoring offshore platforms, pipelines, and refineries for operational safety and efficiency |

| Healthcare & Medical Devices | Simulating patient conditions, equipment usage, and operational workflows in hospitals |

| Smart Cities & Infrastructure | Monitoring traffic, utilities, and infrastructure health in real time for better urban planning |

These sectors adopt digital twins to reduce downtime, improve safety, optimize performance, and extend the operational life of assets—all while lowering costs and enhancing decision-making.

Conclusion

Menta eFPGA enhances digital twin systems in ASICs—whether for power converters, motor control, or automation controllers like PLCs, PACs, and IPCs—by enabling real-time adaptability, in-system reconfigurability, and hardware-level responsiveness. It allows digital twins to evolve alongside changing conditions, support predictive maintenance, and update control logic post-deployment without requiring silicon redesigns. This flexibility extends product lifecycles, improves system reliability, and ensures industrial systems remain secure, efficient, and future-ready in dynamic environments.

Menta’s soft eFPGA IP completely configurable to meet your specific requirements, based on 100% standard cell libraries and is uniquely:

- Foundry-independent – implementable on any process

- Fast to deploy – delivered in RTL in just days

- Cost-efficient – reduced NRE and downstream cost

- Flexible and secure – obfuscated bitstream unique to each device

- Production ready – highest yield, best testability

- Proven – silicon validated across foundries, with radiation-hardened options

- Customizable – supports 3rd party block RAMs, patented DSPs

About Menta

Menta, a pioneering leader in embedded FPGA (eFPGA) technology with over 15 years of proven success, delivers 100% standard-cell, third-party embedded FPGA IP for SoC, ASIC, and ASSP designs. As the only pure-play eFPGA provider offering silicon-proven, synthesis-free IP, Menta empowers semiconductor designers to adapt post-production — enabling rapid updates for bug fixes, customer-specific customizations, evolving standards, or enhanced security.

Our cutting-edge IP is delivered with the Origami toolchain, a seamless solution that generates bitstreams directly from RTL, streamlining design and accelerating time-to-market. Trusted by global semiconductor leaders, Menta transforms chips into agile, future-proof platforms — redefining what’s possible in silicon design.

For more information, please visit the Menta site: http://www.menta-efpga.com/

Contact us at: info@menta-efpga.com

Related Semiconductor IP

- eFPGA Soft IP

- eFPGA IP — Flexible Reconfigurable Logic Acceleration Core

- Heterogeneous eFPGA architecture with LUTs, DSPs, and BRAMs on GlobalFoundries GF12LP

- eFPGA on GlobalFoundries GF12LP

- eFPGA Hard IP Generator

Related Articles

- The Future of Embedded FPGAs - eFPGA: The Proof is in the Tape Out

- Revolutionizing Consumer Electronics with the power of AI Integration

- Streamlining SoC Integration With the Power of Automation

- The Growing Imperative Of Hardware Security Assurance In IP And SoC Design

Latest Articles

- RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

- Emulation-based System-on-Chip Security Verification: Challenges and Opportunities

- A 129FPS Full HD Real-Time Accelerator for 3D Gaussian Splatting

- SkipOPU: An FPGA-based Overlay Processor for Large Language Models with Dynamically Allocated Computation

- TensorPool: A 3D-Stacked 8.4TFLOPS/4.3W Many-Core Domain-Specific Processor for AI-Native Radio Access Networks