Evolution of AMBA AXI Protocol: An Introduction to the Issue L Update

To gain a comprehensive understanding of AMBA® AXI Issue L (AXI-L) protocol update, it is essential to first study the AXI-K specification, as AXI-L is built upon and extends the features introduced in AXI-K. The AXI-L protocol inherits the foundational concepts of AXI-K while introducing enhancements such as credit-based transport and improved flow control mechanisms.

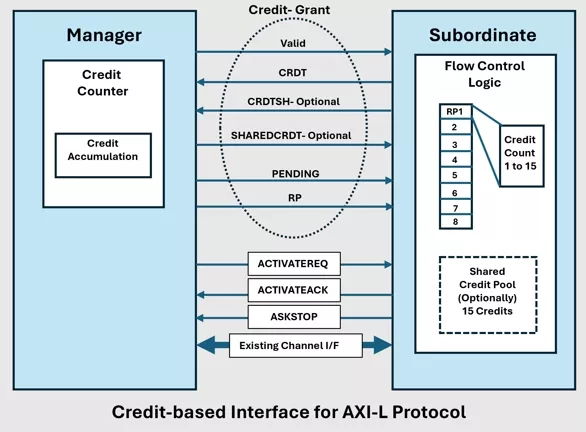

Historically, all versions of the AXI protocol have employed the VALID/READY handshake mechanism across all channels to manage data transfer. However, in AXI-L, AMBA has introduced a new credit-based transport mechanism, replacing the traditional VALID/READY handshake. This marks a significant shift in the protocol's transport methodology.

By adopting the new credit-based transport mechanism introduced in AXI-L, users can benefit from several key advantages over the traditional VALID/READY handshake approach:

|

Attribute |

VALID/READY Handshake |

Credit-Based Transport |

|

Transport Mechanism |

Handshake using VALID and READY signals |

Pre-issued credits for transaction control |

|

Throughput Efficiency |

May suffer from idle cycles due to handshake delays |

Higher throughput with better pipelining |

|

Latency |

Increased latency due to per-transaction handshakes |

Reduced latency by allowing multiple outstanding transactions |

|

Flow Control |

Reactive, based on READY signal |

Proactive, based on available credits |

|

Scalability |

Less efficient at high frequencies or bandwidths |

More scalable for high-performance systems |

|

Predictability |

Less deterministic due to dynamic READY assertion |

More deterministic and predictable behavior |

|

Complexity |

Simpler to implement and debug |

Slightly more complex due to credit management |

|

Use Case Suitability |

Suitable for simpler or lower-bandwidth designs |

Ideal for high-throughput, low-latency, and real-time applications |

AMBA has introduced a new property named AXI_Transport in the AXI5 specification. By default, this property is set to use the traditional VALID/READY handshake mechanism. However, when explicitly configured by the user, it enables the new credit-based transport mechanism. This feature is applicable only to AXI5 and is not supported in earlier versions of the AXI protocol. It is important to note that when the credit-based transport is enabled, the wakeup_signal is not supported.

The flow control rules for the credit-based mechanism are defined in the AMBA specification:

- The minimum number of credits that a receiver can allocate is 1 per Resource Plane (RP).

- The maximum number of credits that a receiver can allocate is 15 per RP, along with an additional 15 shared credits.

To maintain transaction integrity, the following constraints apply:

- For any given write transaction, the AW (Write Address) and W (Write Data) channels must use the same RP number.

- The B (Write Response) and R (Read Data) channels are restricted to a single RP, ensuring consistent response routing.

Additionally, channels that support multiple RPs may optionally implement shared credits. This mechanism enhances buffer utilization efficiency, particularly in scenarios where throughput varies across different RPs. AXI-L explicitly supports shared credit compatibility, allowing for more flexible and efficient flow control in complex system designs.

The key advantages of AXI-L include:

1. Enhanced Transport Efficiency

- Credit-based transport replaces the traditional VALID/READY handshake, reducing latency and improving throughput.

- Enables better pipelining and fewer idle cycles, especially in high-performance systems.

2. Support for Write Interleaving

- Introduction of the Resource Plane allows write interleaving, which was not supported in AXI3.

- Improves memory bandwidth utilization and parallelism in write operations.

3. Shared Credit Mechanism

- Shared credits across multiple RPs allow dynamic buffer utilization, adapting to varying traffic patterns.

- Enhances system flexibility and performance under bursty or uneven workloads.

4. Improved Flow Control

- Flow control is more deterministic and scalable, with clearly defined credit limits.

- Reduces the complexity of managing READY signal timing and backpressure.

5. Optimized for AXI5

- Tailored for AXI5 architecture, aligning with modern SoC requirements such as low latency, high throughput, and real-time responsiveness.

6. Better Resource Utilization

- Credit-based flow control enables predictable resource allocation, improving quality of service (QoS) and system-level scheduling.

AXI-L is fully supported by Cadence VIP. For any additional clarification or technical assistance, users are encouraged to reach out through talk_to_vip_expert@cadence.com.

Learn more about Cadence VIP on the Cadence VIP website.

Related Semiconductor IP

- Verification IP for AMBA AXI

- AMBA AXI STREAM Verification IP

- PCIe 1.1 Controller supporting Root Port, Endpoint, Dual-mode Configurations, with Built-in DMA and Configurable AMBA AXI Interconnect

- AMBA AXI - Validates AXI interface functionality, performance, and compliance

- Simulation VIP for AMBA AXI

Related Blogs

- An Introduction to AMBA CHI Chip-to-Chip (C2C) Protocol

- The Silent Guardian of AI Compute - PUFrt Unifies Hardware Security and Memory Repair to Build the Trust Foundation for AI Factories

- The Architectural Evolution of 16GHz PLLs for Next-Gen AI and SerDes SoCs

- The Evolution of AI and ML- Enhanced Advanced Driver Systems

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk