An Introduction to AMBA CHI Chip-to-Chip (C2C) Protocol

As chip designs grow larger and more complex, they become increasingly difficult to manufacture as a single piece of silicon. Yields (the percentage of properly functioning chips from a semiconductor wafer) decrease significantly with larger die sizes. This limitation of the monolithic chips led to the advent of the multi-die architecture in which the smaller dies (which are easier to produce, resulting in higher yields and lower costs) are housed in a single package. The advantage of the multi-die architecture is that it allows for increased modularity and flexibility. The complexity of the multi-die architecture is that it requires robust, reliable, and standardized interconnect technology for efficient communication between dies (also known as chiplets).

While many vendors utilized proprietary inter-die communication solutions, Arm, in collaboration with a diverse set of industry partners, came up with the AMBA® CHI Chip-to-Chip (C2C) specification, which drew on the very popular existing single-chip AMBA CHI protocol. By extending the CHI specification, CHI-C2C leverages many existing protocol features, making the entire on-chip to off-chip transition straightforward.. The compatibility between the standard CHI and CHI C2C protocols ensures there are no complex transformations between the two, which results in significant latency optimization and enables high-performance, coherent communication in multi-die systems.

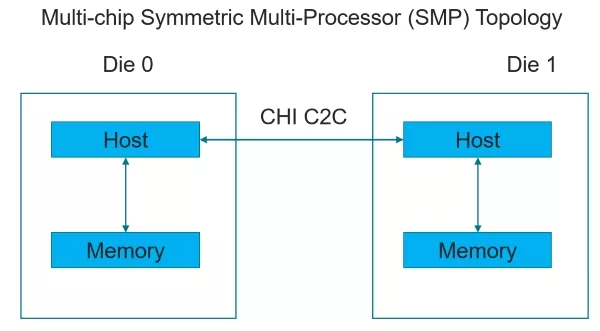

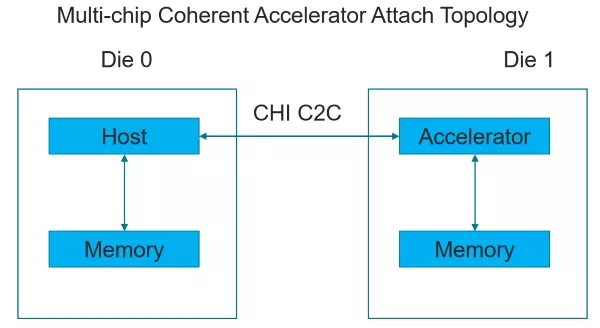

The CHI C2C protocol can be used to enable communication in chip-to-chip as well as chiplet-to-chiplet applications. The supported topologies include the Multi-Chip Symmetric Multiprocessor (SMP) topology, where a number of functionally similar chiplets perform coherent processing, as well as the Coherent Accelerator topology, which enables connection of an I/O coherent or fully coherent device to the system host.

While the CHI C2C specification focuses on the packetization and management of coherent traffic, it requires a transport layer protocol to carry the traffic to its destination. For chiplet-to-chiplet connections, CHI C2C uses Universal Chiplet Interconnect Express (UCIe) as a transport layer, utilizing UCIe's streaming protocol capabilities for standardized die-to-die connectivity. For chip-to-chip connections, Compute Express Link (CXL) is used as a transport layer. The C2C specification defines two container formats for packing/unpacking messages. The first container format, Format X, is compatible with UCIe 256-byte Latency Optimized Mode. The second container format, Format Y, is compatible with CXL 256-byte latency optimized flit format.

The CHI C2C applications are diverse and include AI, data centers, automotive, mobile, and embedded applications. The CHI C2C ecosystem is extensive and includes Design IP and Verification IP solutions from multiple vendors.

Extending its Verification IP offering, Cadence has added the CHI C2C Verification IP, which can be seamlessly used with other Verification IP, such as UCIe VIP, as well as System VIP solutions, such as System Verification Scoreboard. Learn more about Cadence CHI C2C Verification IP on the Cadence VIP website or simply reach out to our Cadence Verification IP experts at talk_to_vip_expert@cadence.com.

Related Semiconductor IP

Related Blogs

- Moving AMBA forward with multi-chip and CHI C2C

- Synopsys AMBA CHI C2C System Verification Solutions

- Cache Coherent Verification - New Features in AMBA CHI

- Reviewing the Latest Arm AMBA ACE5-Lite Protocol Specification Updates

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk