Demystifying Forward Error Correction (FEC) in PCIe 6.0

Introduction

As the industry continues to progress in PCIe, enabling faster and reliable data transfer, with each new generation, PCIe doubles its bandwidth — a change that brings both performance and challenges.

When PCIe 6.0 arrived, one critical feature stood out: Forward Error Correction (FEC). Its inclusion wasn’t optional—it was essential.

To understand why Forward Error Correction (FEC) was introduced in PCIe 6.0, we need to start with the core technical challenge: enabling reliable data transmission at an unprecedented speed of 64.0 GT/s per lane.

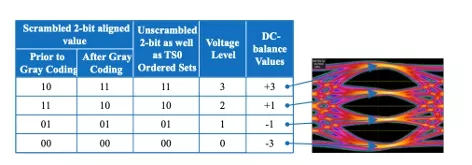

Now, achieving this over existing meant using PAM-4 (Pulse Amplitude Modulation with four levels) signaling instead of traditional NRZ (Non-Return to Zero).

To give you an idea about PAM-4, PAM-4 allows more bits per clock (2 bits instead of 1) but at the cost of:

- Reduced noise margin

- Higher bit error rate (BER)

- Increased sensitivity to signal degradation

Figure: PAM4 signaling at UI level: Voltage levels, 2-bit encoding, and their corresponding DC balance values

Why Are We Talking About PAM-4 Here?

Because without mitigation, PAM-4 would introduce too many transmission errors for reliable communication at PCIe speeds.

To solve this, Forward Error Correction (FEC) was introduced.

FEC adds redundant information to transmitted data, enabling the receiver to detect and correct errors without needing retransmission.

This is where FEC comes in. PCIe 6.0 adopts PAM-4 (Pulse Amplitude Modulation with four levels) signaling, which increases data rates but reduces noise immunity compared to traditional NRZ signaling. To compensate for this reduced signal robustness, PCIe 6.0 incorporates low-latency Forward Error Correction to detect and correct bit errors in real time, without retransmissions or protocol-level recovery.

In PCIe 6.0, FEC ensures that even with a higher BER due to PAM-4, data integrity is preserved. FEC works by encoding data at the transmitter with extra bits using a linear block code and then checking and correcting errors at the receiver using this redundant data.

Introducing FEC has a huge impact on overall performance, latency, and reduced cost. FEC makes 64 GT/s possible with PAM-4 while maintaining the reliability for applications using huge data. While FEC adds a small amount of latency and logic overhead, it’s minimal compared to the benefit it brings.

What Would PCIe Gen6 Be Like Without FEC?

If PCIe 6.0 had tried to run at 64 GT/s PAM-4 without FEC, unacceptably high bit error rates would occur due to PAM-4’s low noise margin and system designers would need costlier and more complex signal integrity solutions—more exotic PCB materials, advanced connectors, or very short channel lengths.

Alternatively, PCIe 6.0 would be forced to use NRZ signaling, reducing bandwidth to 32 GT/s or rely on retransmission, leading to significant latency and complexity.

In effect, PCIe 6.0 wouldn’t be possible at 64 GT/s over realistic links without FEC. It would fail to meet the core requirement of doubling bandwidth per generation while maintaining power, cost, and compatibility targets.

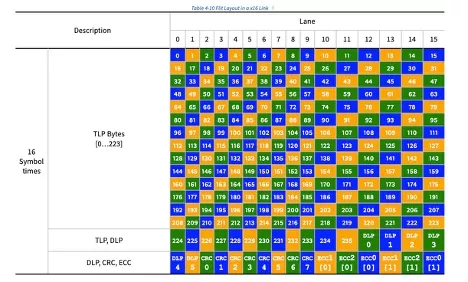

The FEC is a 3-way interleaved ECC, with each ECC code capable of correcting a single byte error. The interleaving is done

so that a burst error of up to 16 bits in any lane does not impact more than a byte in each interleaved ECC code word.

Each of the interleaved ECC has a different color. Thus, all blue colored bytes [e.g., 0, 3, 6, 9,…, 231, 234, DLP1, DLP4, CRC1, CRC4, and CRC7] are part of ECC Group 0 and are covered by the two blue colored ECC0[0] and ECC0[1] bytes (which are placed in the last symbol of the flit in lanes 12 and 15 respectively).

Conclusion

FEC in PCIe Gen6 is not just an addition—it is a fundamental necessity. As I mentioned in the beginning, “Its inclusion wasn’t optional—it was essential”.

By compensating for the increased error susceptibility of PAM-4 signaling, FEC ensures high data integrity, keeps latency low, and allows PCIe to continue scaling bandwidth effectively. Without it, PCIe Gen6 would either operate much more slowly or be impractically expensive and complex to implement.

Learn More

- For more information on how Cadence PCIe Verification IP and TripleCheck VIP enable users to confidently verify IDE, see our VIP for PCI Express, VIP for Compute Express Link, and TripleCheck for PCI Express

- For more information on PCIe in general, and on the various PCI standards, see the PCI-SIG website

- If you have more feedback or need more information, reach out to us at talk_to_vip_expert@cadence.com

Related Semiconductor IP

- PHY for PCIe 6.0 and CXL

- PCIe 6.0 PHY, SS SF2A x4 1.2V, N/S for Automotive, ASIL B Random, AEC-Q100 Grade 2

- PCIe 6.0 PHY G2 , SS SF4X x4, North/South (vertical) poly orientation

- PCIe 6.0 PHY, TSMC N3A x4 1.2V, North/South (vertical) poly orientation for Automotive, ASIL B Random, AEC-Q100 Grade 2

- PCIe 6.0 Integrity and Data Encryption Security Module

Related Blogs

- Verification of Light Weight Forward Error Correction (FEC) and Strong Cyclic Redundancy Checks (CRC) feature in PCIe 6.0

- Programmable Hardware Delivers 10,000X Improvement in Verification Speed over Software for Forward Error Correction

- PCIE 6.0 vs 5.0 - All you need to know

- Big Innovations Double the Data Rate to 64 GT/s with PCIe 6.0

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk