A Comparison on Different AMBA 5 CHI Verification IPs

A Complete Vendor-by-Vendor Analysis

Introduction

In today’s semiconductor world, system-on-chip (SoC) designs face a very specific challenge: maintaining cache coherency and consistent data sharing across dozens of heterogeneous components. Modern SoCs often integrate CPUs, GPUs, AI accelerators, and high-bandwidth memory controllers on the same die. Without a robust and standardized coherency protocol, these blocks can end up working on stale or inconsistent data, leading to subtle bugs, performance bottlenecks, or even system failures.

The AMBA Coherent Hub Interface (CHI), developed by Arm, was designed to address this challenge. It has become a widely adopted standard for ensuring data consistency and cache coherency across multiple cores in high-performance SoCs.

However, simply building a SoC that supports CHI is not enough. Because CHI is a detailed and sophisticated protocol, the design must be verified thoroughly before silicon tape-out to catch subtle bugs that could compromise functionality. This is where Verification IPs (VIPs) come in—accelerating and simplifying the verification process.

While several vendors offer CHI VIP solutions, their features, strengths, and weaknesses vary greatly, making it difficult for engineering teams to choose the right fit for their project needs.

To compare the leading CHI VIP offerings in the market—based on protocol coverage, debugging ecosystems, automation, environment support, strengths, and weaknesses—and highlight where each vendor solution is best suited.

By presenting a structured, side-by-side analysis, this blog aims to help design and verification teams make informed decisions when selecting CHI VIP, saving time, reducing verification risks, and ensuring smoother SoC development.

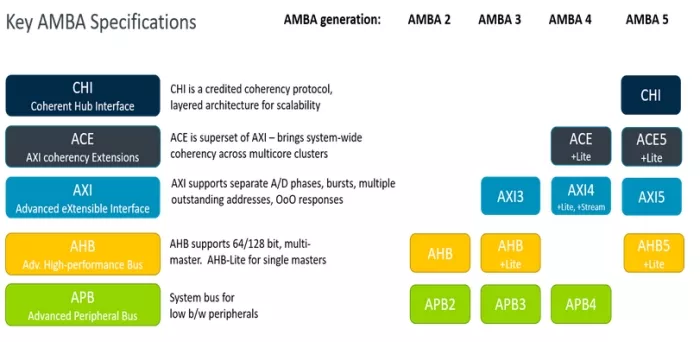

Figure 1: Bus Protocols in AMBA Family

Contextual Foundation: Arm’s CoreLink CMN-600

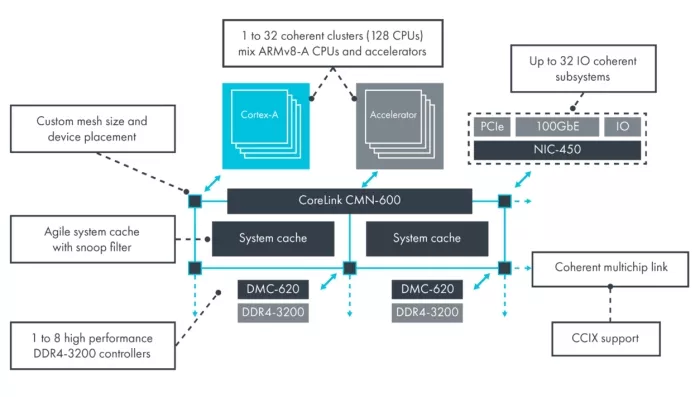

To put CHI VIPs into context, it helps to look at a real CHI interconnect implementation. One of the most widely adopted is Arm’s CoreLink CMN-600, a scalable and configurable coherent mesh interconnect that is commonly used in networking and enterprise-class SoCs.

The CMN-600 is designed to meet Power, Performance, and Area (PPA) targets for high-end compute platforms. It supports 1–64 processor clusters, GPU/AI accelerators, I/O subsystems, and multiple memory controllers connected over a mesh fabric of crosspoints (XPs). The topology is highly configurable using Arm’s Socrates™ Tooling, allowing custom mesh size, placement of devices, and optional System Level Cache (SLC) and Snoop Filter (SF) slices for better scalability.

From a protocol standpoint, CMN-600 is fully compliant with AMBA 5 CHI Issue B and C, and implements advanced CHI features such as:

- Far Atomics and Direct Data Transfer (DMT/DCT) for lower latency

- Cache stashing to improve data locality

- Separate Read Data and Comp responses for higher concurrency

- Combined CompAck with WriteData optimizations

At the system level, it includes:

- QoS regulation for shaping traffic profiles

- RAS features (ECC, SECDED, data poisoning) for enterprise reliability

- Debug & Trace infrastructure for system observability

In terms of scalability:

- Up to 64 Request Nodes (RN-F) for fully coherent masters (CPU clusters, GPUs, accelerators)

- Up to 16 memory controllers (SN-F)

- Up to 32 I/O coherent Request Nodes (RN-I/D) for ACE-Lite masters

- Optional Coherent Multichip Link (CML) with CCIX support, enabling up to 4 SoCs in a single coherent system

Figure 2: CoreLink CMN-600 [5]

Vendor-by-Vendor Comparison

In this section we will compare the leading AMBA 5 CHI Verification IP (VIPs) in the industry across key evaluation metrics. The comparison focuses on protocol coverage, unique features, debugging ecosystems, automation levels, environment support, strengths, and weaknesses. These metrics were chosen because they directly affect verification speed, ease of integration, and coverage quality. For example, a strength might be broad protocol revision coverage or advanced debug GUIs that accelerate root-cause analysis, while a weakness could be higher licensing costs, a steep learning curve, or lack of support for the latest CHI revisions. By analyzing each vendor’s offering against the same set of criteria, we aim to provide a clear, side-by-side perspective that helps you identify which VIP best fits different use cases.

1. Synopsys

Synopsys Verification IP (VIP) for Arm AMBA CHI provides a comprehensive set of protocol, methodology, verification and productivity features, enabling users to achieve accelerated verification closure of interconnects and interfaces. Here is the reference link.

Protocol Coverage:

- Supports AMBA 5 CHI Issues A–G.

- Provides Request Node (RN), Secondary Node (SN) agents, and a CHI System Monitor.

- Includes built-in cache (RN) and memory (SN) models for realistic simulation.

Key Features:

- VC SoC AutoTestBench – Improves productivity by automatically generating a SystemVerilog UVM testbench from DUT information.

- CHI System Environment (Env) – Provides a pre-integrated setup with RN, SN, interconnect, and monitor agents.

- System Monitor – Validates coherency and data integrity across RN/SN ports.

- Seamless Integration – Works smoothly with other Synopsys AMBA VIPs for end-to-end verification.

- Supports simulation, formal analysis, and hardware acceleration platforms.

Strengths:

- Comprehensive protocol coverage.

- Automation boosts productivity.

- Strong system-level validation.

Weaknesses:

- Steep learning curve.

- Licensing is expensive.

Best Fit:

Tier-1 semiconductor teams require advanced automation, fast closure, and system-level focus.

2. Cadence

Cadence provides a mature and comprehensive Verification IP (VIP) for the Coherent Hub Interface (CHI) specification, which is part of the Arm AMBA family of protocols. Here is the reference link.

Protocol Coverage:

- Supports AMBA 5 CHI Issues A–H.

- Covers link, network, and protocol layers.

- Supports RN-F/D/I, HN-F/D/I/MN and SN-F/I.

- Includes embedded cache model (RN) and memory model (SN) models.

- Dummy CHI-based interconnect support. When interconnect is not present, the active HN-F can generate snoop requests and respond to RN-F commands

Key Features:

- Bus Functional Model (BFM) with protocol checkers.

- Constrained-random traffic generation with predefined error injection.

- Packet Tracker and Waveform Debugger for deep traceability.

- Channel Delay – Control timing of individual flits.

- Cache Model & Access – Simulates L2 cache in CHI RN-F and runtime backdoor cache access.

- Callbacks access at multiple queue points for scoreboarding and data manipulation

- Broadest methodology support (SystemVerilog, UVM, OVM, SystemC, Specman E).

- Supports simulation, formal analysis, and hardware acceleration platforms.

- Provides comprehensive checking and coverage model

Strengths:

- Widest revision coverage (A–H).

- Cache modeling and delay control for more realistic verification.

- Best-in-class debugging ecosystems.

Weaknesses:

- Expensive.

- Full benefits tied to Cadence toolchains.

Best Fit:

SoC teams require debug-rich analysis, multi-environment support, and revision-complete compliance.

3. SmartDV

SmartDV’s AMBA CHI Verification IP is built to verify high-performance, cache-coherent interconnects in advanced SoC designs through simulation. Fully compliant with the AMBA CHI protocol specification, it enables accurate and efficient validation of scalable, high-throughput system architectures.Here is the reference link.

Protocol Coverage:

- Fully compliant with CHI Issues A-D.

- Supports Master, Slave, Interconnect, Monitor, Checker.

- Supports RN-F/D/I, HN-F/I/MN and SN-F/I.

Key Features:

- Broad simulator/methodology support (SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E).

- Smart ViPDebug GUI – GUI based debugger to speed up debugging.

- Cache models support in Master and Interconnect with programmable behavior and monitor has backdoor access to cache models.

- Advanced support: DMT(Direct memory transfer), DCT(Direct cache transfer), DVM ops, speculative reads, snoop filtering.

- Programmable Protocol flit delays and different channels delays.

- Error injection during link initialization/transfers.

- Built-in coverage, logging, and performance reporting.

- Callbacks in Master, Slave, Interconnect and Monitor for various events.

Strengths:

- Broadest environment/language compatibility.

- GUI debugging improves productivity.

Weaknesses:

- Smaller presence compared to Synopsys/Cadence.

- Latest revision not available

Best Fit:

Teams seeking multi-environment flexibility, fine-grain control, and error-injection capabilities.

4. Truechip

Truechip’s AMBA5 CHI Verification IP provides an effective & efficient way to verify the components interfacing with AMBA 5 CHI bus of an IP or SoC. Truechip’s AMBA5 CHI VIP is fully compliant with standard AMBA5 CHI specifications from ARM. Here is the reference link.

Protocol Coverage:

- Fully compliant with the latest CHI Issue.

- Supports RN-F/D/I, HN-F/I and SN-F/I.

- Works across Crossbar, Ring, Mesh topologies.

Key Features:

- Lightweight plug-and-play VIP – Minimizes design cycle impact and enables quick adoption.

- Available in native System Verilog (UVM/OVM/ VMM) and Verilog.

- GUI for easy analyzing packet debugging and decoding

- Protocol support: DMT, DWT, DCT, DVM ops, REM, MPAM, PBHA.

- Bus Monitor – Offers transaction statistics and protocol assertions for compliance and coverage.

- AMBA 5 CHI NoC Scoreboard – Monitors and validates NoC transactions for compliance and data integrity.

Strengths:

- Easy adoption and lightweight.

- Exhaustive compliance suites included.

Weaknesses:

- Less advanced automation/debug ecosystem.

- Focused more on compliance than performance stress.

Best Fit:

Startups looking for budget-friendly VIPs with fast integration and compliance focus.

5. Avery Design Systems (Siemens EDA – Avery VIP)

Enable system-on-chip (SoC) and IP developers to perform comprehensive functional verification of their IP and SOCs. Avery Verification IP for AMBA incorporates the full range of AMBA bus protocols (AXI4 – Full, Lite, Stream, AXI3, AHB, APB, CHI) master, slave and interconnects functionalities and ensure compliance to the AMBA standards.. Here is the reference link.

Protocol Coverage:

- Fully compliant with CHI Issues A-E.

- Supports master, slave, and interconnect models in active and passive mode monitors.

- Includes CHI home node agent interconnect with directory, request, and slave agents.

- Supports CXS.B interface for CXL/CCIX-CHI bridging, enabling unit-level verification.

Key Features:

- Available in native System Verilog and UVM.

- Robust protocol checks, coverage, error injection, and performance metrics.

- Passive monitors for snoop response verification.

- Cache state trackers and transaction-level protocol trackers for improved debugging.

- Integration with ARM FastModels for HW/SW co-verification.

- Extended support for multi-path, multi-link topologies and more complex coherency environments.

- Cache models support in Master and Interconnect and have backdoor access to cache models.

Strengths:

- Strong compliance and interoperability validation, often used for pre-silicon certification.

- Comprehensive debug features (cache tracker, protocol analyzer-like features).

Weaknesses:

- Focused more on compliance and debug than on acceleration/emulation.

- May require more customization for performance stress verification compared to Synopsys/Cadence.

Best Fit:

- Teams validating multi-vendor SoCs, chiplet-based designs.

- Ideal for organizations needing robust coherency test suites and extended coverage across ACE/CHI/CXL/CCIX ecosystems.

Comparison Summary

| Vendor | Protocol Coverage | Debugging & Analysis Features | Automation | Environment & Language Support |

| Synopsys | Issue A-G | System Monitor, Env integration | High – AutoTestBench generation, integrated environments, accelerated coverage closure | UVM, SystemVerilog, Acceleration, Formal |

| Cadence | Issue A-H | Packet Tracker, waveform dbg | High – Constrained-random traffic, error injection, callbacks, built-in coverage | UVM, OVM, SystemVerilog, Specman E, Acceleration, Formal |

| SmartDV | Issue A-D | Smart ViPDebug GUI, cache visibility | Medium – Built-in coverage, programmable flit/channel delays, error injection | UVM, OVM, VMM, SystemC, Specman E |

| Truechip | Latest Issue | GUI packet decoder, NOC scoreboard | Medium – Lightweight plug-and-play setup, compliance suites included | SystemVerilog, Verilog |

| Avery Systems | Issue A-E | Cache trackers, compliance monitors | Medium – Constrained-random traffic, coverage models, error injection | SystemVerilog UVM |

Feature Parity & Gaps in Coverage

Latest CHI-revision Support

- Synopsys – First to deliver CHI-G support.

- Cadence – Broadest revision coverage (A–H).

- SmartDV – Strong CHI-D support.

- Truechip – Support Latest Spec

- Avery – Support CHI A-E

Hardware Acceleration

- Cadence & Synopsys – Comprehensive support for simulation acceleration and hardware acceleration, suited for very large SoCs.

- SmartDV & Truechip & Avery – Primarily simulation-oriented.

Formal Verification Hooks & Assertions

- Cadence & Synopsys – Provide extensive assertion libraries and protocol checkers compatible with formal verification.

- Truechip – Focus mainly on simulation-based checkers and Assertions.

- SmartDV – Focus mainly on simulation-based checkers.

- Avery – Provides SystemVerilog assertions and compliance suites (more focused on interoperability).

Market Trends & Future Outlook

CHI-G adoption: Vendors racing to support latest issue CHI-G.

System-level verification: SoCs increasingly combine CHI with AXI, ACE, CXL, and CCIX; demand for multi-protocol VIP is rising.

Acceleration/emulation: Simulation alone is insufficient; hardware acceleration is becoming mandatory.

Compliance & interoperability: More vendors seek formal certification and interoperability validation before tape-out.

Company Contributions:

TEAM-REDWOOD

The team worked on upgrading the system interconnect from a CHI Version 1 block to a CHI Version 2 block, a critical enhancement to support next-generation performance and scalability. The CHI block included dedicated request and response bridges, an embedded I/O-coherent Home Node Interface for transforming CHI transactions into AXI requests to multiple targets, and an I/O-coherent Request Node Interface for initiating transactions.

A significant part of the effort involved adapting the architecture to handle multiple CHI links, which required extensive modifications to address tables, routing logic, and internal decoding structures. To ensure reliable operation, the team also implemented strategic pipeline stages that optimized data flow and helped achieve timing closure across the block. Alongside these architectural changes, conducted rigorous verification, bug fixes, and validation, ensuring the upgraded block delivered both robustness and performance.

TEAM-WILLOW

The team focused on functional coverage development, building detailed coverage models for the requester interface and implementing layer-by-layer coverage on the CHI interface.

TEAM-REDOAK

CHI Requester without snoop:The CHI requester was implemented using a memory-mapped AXI4 path, allowing CPU-initiated register writes over AXI to be seamlessly converted into CHI requests. The design incorporates channelized communication for requests, responses, and data transfers, managed by a link-layer state machine that ensures reliable handshakes and flow control. Operating in a requester-without-snoop configuration, it provides full compliance with CHI protocol requirements at both the link and higher protocol layers, while offering a lightweight and efficient requester solution for non-coherent use cases.

CHI Home IP and VIP development: Developed to provide robust support across the protocol, network, and link layers, the home node implementation includes features such as link initialization skip/retry mechanisms, configurable credit control (both dynamic and pre-allocated), and full compatibility with all ARM AMBA 5 CHI data widths. The design supports advanced transaction handling, including retries, cancellations, multiple outstanding non-snoopable operations, and atomic transactions, ensuring both flexibility and compliance in verification and integration environments.

CHI Home Node Development and Verification: Designed and verified to provide robust support across the protocol, network, and link layers, the home node implementation incorporates link initialization skip/retry mechanisms and configurable credit control (dynamic and pre-allocated). The solution was thoroughly verified to ensure correct handling of advanced transactions, including retries, cancellation and atomic transactions, delivering both flexibility and compliance for integration into complex systems.

References

[1] “Verification IP for AMBA CHI | Synopsys,” Synopsys.com, 2025. https://www.synopsys.com/verification/verification-ip/amba/amba-chi.html (accessed Aug. 26, 2025).

[2] “AMBA VIP Solutions,” Cadence.com, 2025. https://www.cadence.com/en_US/home/tools/system-design-and-verification/verification-ip/simulation-vip/amba.html#amba-chi (accessed Aug. 26, 2025).

[3] “AMBA 5 CHI Verification IP,” Smart-dv.com, 2025. https://www.smart-dv.com/vip/chi.html (accessed Aug. 26, 2025).

[4] Truechip Solutions, “AMBA 5 CHI Verification IP | Truechip VIPs | Truechip,” Truechip.net, 2024. https://www.truechip.net/details/chi-5/660877

[5] “CoreLink CMN-600,” Arm.com, 2025. https://developer.arm.com/Processors/CoreLink%20CMN-600 (accessed Aug. 26, 2025).

[6] Siemens Digital Industries Software, “Avery Verification IP for AMBA,” Data sheet, 85926-D2 (Mar. 2024). [Online]. Available: https://static.sw.cdn.siemens.com/siemens-disw-assets/public/41nl6PgHM8wD8Qp1QaAdhi/en-US/siemens-sw-avery-verification-ip-for-amba-fs-85926-d2.pdf

Related Semiconductor IP

- AMBA 5 CHI Verification IP

- AMBA 5 CHI Verification IP

- AMBA 5 CHI Assertion IP

- Simulation VIP for AMBA CHI

- AMBA 5 CHI Synthesizable Transactor

Related Blogs

- Synopsys Introduces the Industry's First Verification IPs for Arm AMBA 5 AXI-J and APB-E

- Cache Coherent Verification - New Features in AMBA CHI

- Synopsys Introduces the Industry's First Verification IP for Arm AMBA 5 CHI-F

- Synopsys AMBA CHI C2C System Verification Solutions

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk