Building Blocks IP

Welcome to the ultimate Building Blocks IP hub! Explore our vast directory of Building Blocks IP

All offers in

Building Blocks IP

Filter

Compare

353

Building Blocks IP

from

48

vendors

(1

-

10)

-

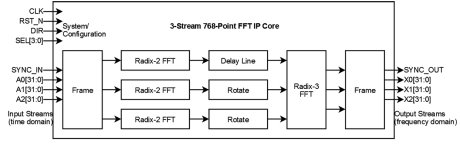

MixedRadix FFT IP Core

- The MixedRadix FFT IP Core uses a modular combination of radix2, 3, 5, and 7 Fast Fourier Transform (FFT) pipelined engines to provide discrete transforms on data frames or continuous data streams, with sample rate up to the maximum clock frequency.

- The engines are arranged to provide the most beneficial resource usage and data ordering for the system.

-

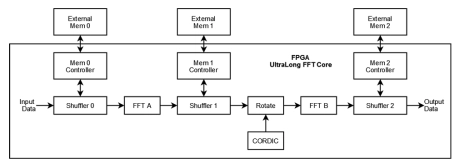

UltraLong FFT

- The UltraLong FFT IP Core uses an efficient Fast Fourier Transform (FFT) algorithm to provide multimillion-point discrete transforms on data frames or continuous data streams.

- This structure utilizes state-of-the-art off-chip memory technology and N1- and N2-length pipelined radix-2 FFT engines with an additional rotation stage to perform N=N1xN2 transform lengths, from 1K to 64M points.

-

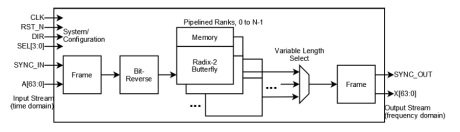

Pipelined Floating Point FFT IP Core

- Any radix-2 length

- Variable length option for runtime per-transform length select

- Clock rates to 400MHz in Virtex-5

- Fixed or floating point math

-

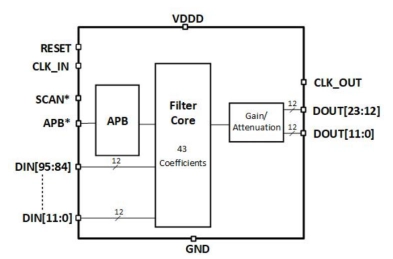

12-bit 250MHz Decimation filter with 43 taps

- Programmable Coefficients

- Programmable gain/attenuation at the output

- 4X Decimation Factor

-

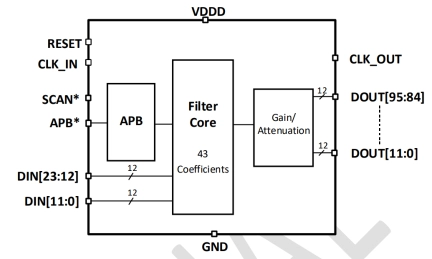

12-bit 250MHz interpolation filter with 43 taps on TSMC 16nm

- The ODT-DSP-INT-43T250M-T16 is a 12-bit 250MHz interpolation filter with 43 taps in a 12/16nm CMOS process.

- The 43 Tap interpolation filter increases output data rate (fDOUT) to the DAC by four relative to its original input data rate(fDIN).

-

Fast Fourier Transform IP Core

- Supports forward and inverse complex FFT

- Supports transform length (N) from 23 to 2¹⁶

- Supports scaled or unscaled IFFT output

- Implemented as pipelined streaming IO architecture

-

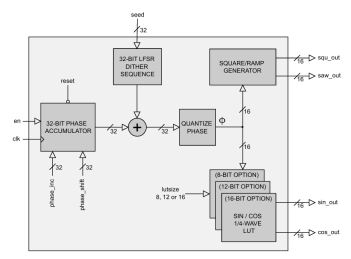

Direct Digital Synthesizer / Periodic waveform generator

- The DDS IP Core is a high-precision Direct Digital Synthesizer2 used for the generation of periodic waveforms.

- On each rising-edge of the sample clock and when the clock-enable is high, the phase in the phase accumulator is incremented by the value phase_inc.

- This phase is quantized to 16-bits and passed as an address to a look-up table which converts the phase into a waveform.

-

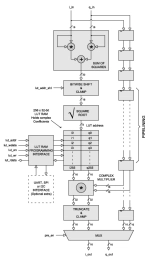

RF Power Amplifier Precorrection System

- DPSYS is a complete Digital Precorrection (Predistortion) system designed to compensate for the non-linear characteristic of a high-power RF Amplifier.

- The system is capable of adjusting both the gain and phase of a complex input signal.

- This is achieved by means of a complex multiplication of the input with a complex polynomial function stored in the LUT. Complex inputs are sampled on the rising edge of clk when en is high.

-

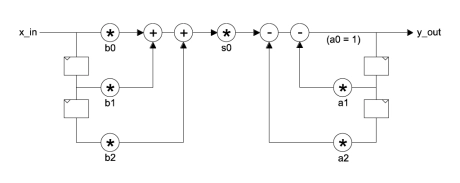

IIR Filter Second-Order-Section

- 2nd order IIR filter sometimes referred to as a 'bi-quad'.

- Internally, it has a fully pipelined architecture permitting the highest possible sample rates for IIR filtering.

- The SOS block is modular allowing any number of SOS blocks to be joined in series to implement higher order IIR filters.

-

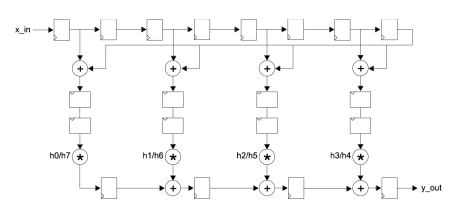

Generic high-speed FIR Filter with symmetry

- FIR filter designed for high sample rate applications with symmetrical coefficients and an even or odd number of taps.

- Features configurable coefficients and data width. Design uses only half the number of multipliers compared to a normal FIR implementation.

- Matlab®, FDAtool and Simulink® compatible.