Other

All offers in

Other

Filter

Compare

140

Other

from

53

vendors

(1

-

10)

-

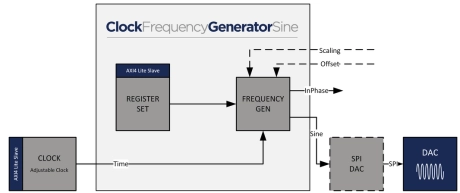

Sine Wave Frequency Generator

- The Sine Wave Frequency Generator is a time and frequency aligned sine wave frequency generator allowing any frequency to be generated between 1Hz and 200kHz adjustable in 1Hz steps.

- It uses the vendor's Adjustable Clock core as source for source synchronous frequency generation. It provides either a parallel DAC interface or a serial highly configurable SPI interface to access a DAC.

-

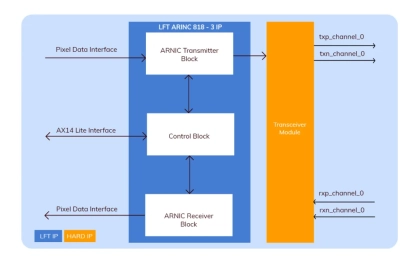

ARINC 818-3 IP Core

- Compliant to ARINC818-3 Specification. The max speed supported is 28 Gbps.

- Built on Fiber Channel Audio Video protocol.

- Point-to-Point Video/Data Transmission support using 64B/66B and 256B/257B Encoding over the serial link.

- Supports both optical and electrical links.

-

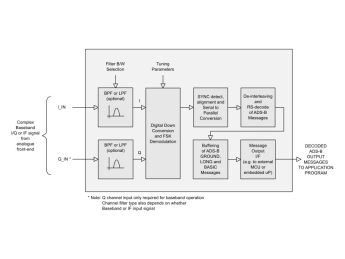

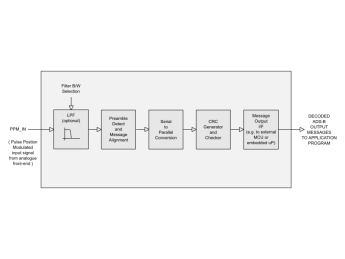

ADS-B 978 MHz (UAT) Receiver

- ADS-B (UAT) receiver offers a comprehensive solution for the reception of flight, traffic and weather information.

- Compatible with all FPGA, SoC and ASIC devices, the circuit has been design proven and field tested, clocking over 500 flight hours.

- Complies with the RTCA DO-282B.

-

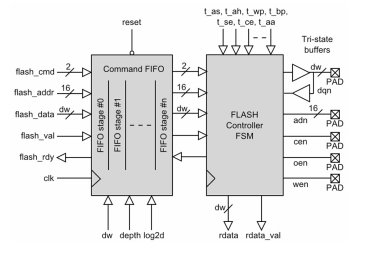

Parallel FLASH Memory Controller

- JEDEC® compliant FLASH memory controller ideal for interfacing to a wide range of parallel FLASH memory components such as the popular SST39 series from Microchip®.

- Features a fully synchronous command interface and a set of configurable timing parameters for compatibility with different devices.

-

ADS-B 1090 MHz (ES) Receiver

- ADS-B (ES) receiver offers a comprehensive solution for the reception of flight and traffic information.

- Compatible with all FPGA, SoC and ASIC devices, the circuit has been design proven and field tested, clocking over 500 flight hours.

- Complies with RTCA DO-260B.

-

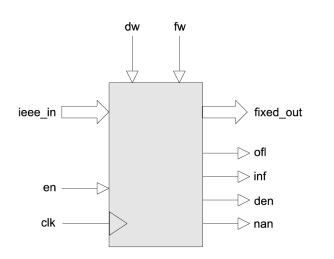

Floating-point to Fixed-point Converter

- Converts 32-bit floating-point numbers to fixed-point representation. The fixed-point output has a configurable word and fraction width.

- Floating-point inputs are based on the IEEE 754 standard. The design features a high-speed, fully pipelined architecture with a 2 clock-cycle latency.

-

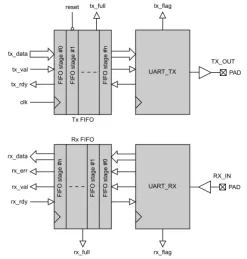

UART Serial Interface Controller

- The UART_CONT IP Core is a robust UART-compliant serial interface controller capable of receiving and transmitting bits serially.

- It has a configurable data payload from 5 to 8-bits (with or without parity) and supports either 1 or 2 stop bits.

-

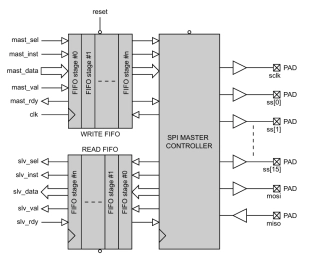

SPI Master Serial Interface Controller

- The SPI_MASTER IP Core is an SPI compliant serial interface controller capable of driving up to 16 different slave devices in full-duplex operation.

- The controller receives data and instructions via the master instruction interface.

- These instructions are then processed by the controller core in order to generate the appropriate signals on the SPI bus.

-

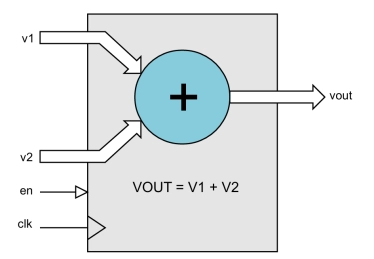

Floating-point Adder

- High-speed fully pipelined 32-bit floating-point adder/subtractor based on the IEEE 754 standard.

- Results have a latency of 4 clock cycles. Ideal for floating-point pipelines, arithmetic units and processors.

-

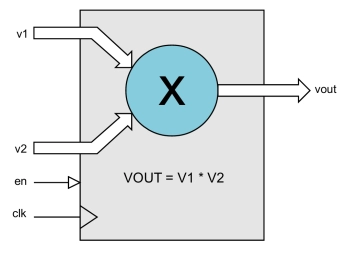

Floating-point Multiplier

- High-speed fully pipelined 32-bit floating-point multiplier based on the IEEE 754 standard.

- Results have a latency of only 4 clock cycles. Ideal for floating-point pipelines, arithmetic units and processors.