DSP & Math IP

Welcome to the ultimate DSP & Math IP hub! Explore our vast directory of DSP & Math IP

All offers in

DSP & Math IP

Filter

Compare

813

DSP & Math IP

from

98

vendors

(1

-

10)

-

LunaNet AFS LDPC Encoder and Decoder IP Core

- Rate 1/2

- GNSS, AFS

- Subframe 2/3/4

- Low implementation loss

-

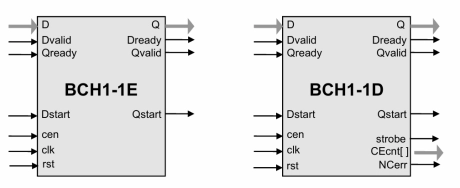

Very Low Latency BCH Codec

- High performance, low latency

- Small size (75K gates for k=298, t=4) configuration, the core uses just 17K gates in ASIC)

- Entirely self-contained (no external RAM required)

- Data inputs and outputs have flip-flops attached to the pins

-

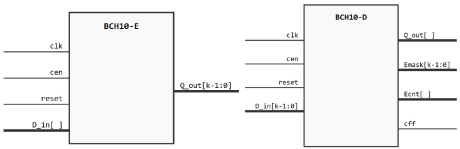

Parameterizable compact BCH codec

- Highly parameterizable

- Very low area (in the largest, n = 511 t = 16 configuration, the core uses just 17K gates in ASIC)

- Entirely self-contained (no external RAM required)

-

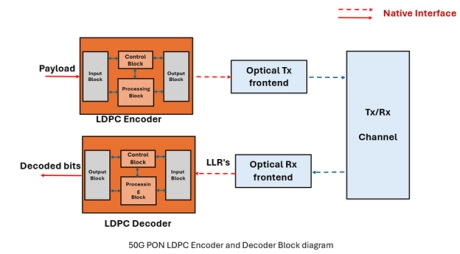

50G PON LDPC Encoder/Decoder

- Fully compliant with ITU-T G.9804 LDPC specifications

- Supports downstream and upstream FEC requirements - LDPC (17280, 14592)

- Supports Throughput up to 50 Gbps

- Supports both hard-decision and soft-decision decoding

-

SDA OCT Encoder and Decoder

- The SDA OCT Encoder handles the construction of Over-The-Air (OTA) frames as indicated in the standard, a preamble followed by a header and payload data, with both fields being protected by cyclic redundancy check (CRC) and forward error correction (FEC).

- The SDA OCT Decoder performs the synchronization of the Over-The-Air (OTA) frame and then decodes the header and payload data within the frame.

-

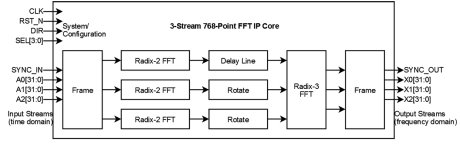

MixedRadix FFT IP Core

- The MixedRadix FFT IP Core uses a modular combination of radix2, 3, 5, and 7 Fast Fourier Transform (FFT) pipelined engines to provide discrete transforms on data frames or continuous data streams, with sample rate up to the maximum clock frequency.

- The engines are arranged to provide the most beneficial resource usage and data ordering for the system.

-

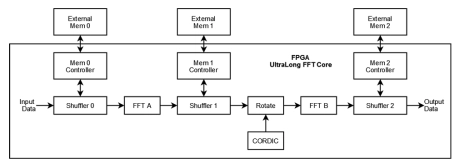

UltraLong FFT

- The UltraLong FFT IP Core uses an efficient Fast Fourier Transform (FFT) algorithm to provide multimillion-point discrete transforms on data frames or continuous data streams.

- This structure utilizes state-of-the-art off-chip memory technology and N1- and N2-length pipelined radix-2 FFT engines with an additional rotation stage to perform N=N1xN2 transform lengths, from 1K to 64M points.

-

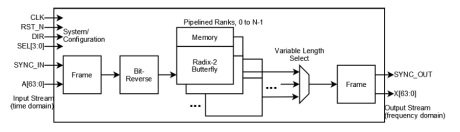

Pipelined Floating Point FFT IP Core

- Any radix-2 length

- Variable length option for runtime per-transform length select

- Clock rates to 400MHz in Virtex-5

- Fixed or floating point math

-

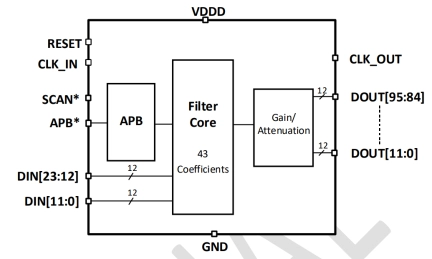

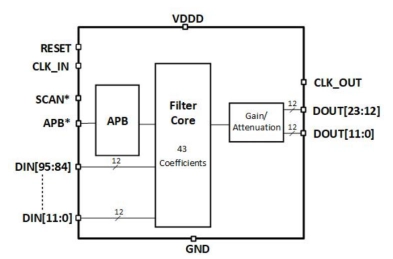

12-bit 250MHz Decimation filter with 43 taps

- Programmable Coefficients

- Programmable gain/attenuation at the output

- 4X Decimation Factor

-

12-bit 250MHz interpolation filter with 43 taps on TSMC 16nm

- The ODT-DSP-INT-43T250M-T16 is a 12-bit 250MHz interpolation filter with 43 taps in a 12/16nm CMOS process.

- The 43 Tap interpolation filter increases output data rate (fDOUT) to the DAC by four relative to its original input data rate(fDIN).