IoT Processor IP Cores

Welcome to the ultimate IoT Processor IP hub! Explore our vast directory of IoT Processor IP Cores.

The IoT Processor IP Cores are ideal for M2M protocol stack and baseband PHY control, including LTE Cat-NB1, Cat-M1, Sigfox, LoRa, Wi-Fi 802.11n, 802.11ah, Bluetooth, Bluetooth Low Energy, and Zigbee/Thread. They also support positioning and motion-sensing functions, including GNSS (GPS, Beidou, GLONASS, Galileo), fusion of multiple indoor positioning and activity sensors, voice activation, and sound processing.

All offers in

IoT Processor IP Cores

Filter

Compare

11

IoT Processor IP Cores

from

7

vendors

(1

-

10)

-

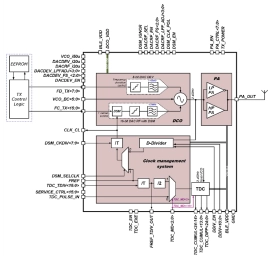

BLE Advertising Transmitter RF Frontend

- Global Foundries Embedded EEPROM 130nm

- Operating temperature range –40…+85 °C

- Output power adjustment ability

- High precision output frequency without reference frequency

-

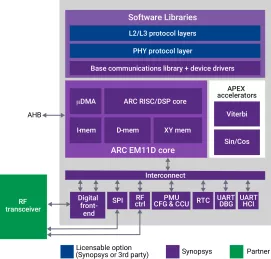

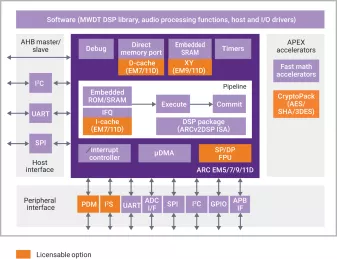

ARC IoT Communications IP Subsystem

- Integrated, pre-verified hardware and software IP subsystem

- ARC EM11D processor with DSP extensions delivers extremely low gate count and highly efficient processing performance

- Hardware accelerators for key communications functions such as Viterbi decoding dramatically reduce cycle counts and energy consumption

- Integrated peripherals provide a wide range of SoC connectivity options for SoC/MCUs

-

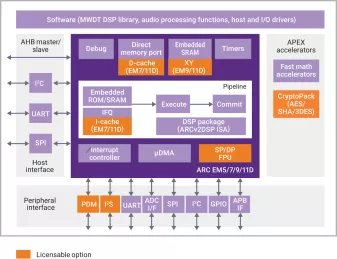

Data Fusion IP Subsystem

- Integrated, pre-verified hardware and software IP subsystem

- ARC EM processors with cache and DSP extensions deliver extremely low gate count and highly efficient processing performance

- Extensive library of software DSP functions enable sensor signal processing

- Hardware accelerators boost performance efficiency and reduce power consumption

-

ARC Data Fusion Voice/Speech Option

- Integrated, pre-verified hardware and software IP subsystem

- ARC EM processors with cache and DSP extensions deliver extremely low gate count and highly efficient processing performance

- Extensive library of software DSP functions enable sensor signal processing

- Hardware accelerators boost performance efficiency and reduce power consumption

-

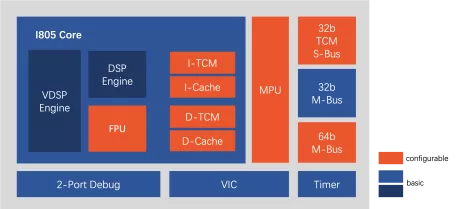

AIoT processor with vector computing engine

- Instruction set: T-Head ISA (32-bit/16-bit variable-length instruction set);

- Pipeline: 4-stage sequential pipeline;

- General register: 32 32-bit GPRs; 16 128-bit VGPRs;

- Cache: I-Cache: 8 KB/16 KB/32 KB/64 KB (size options); D-Cache: 8 KB/16 KB/32 KB/64 KB (size options);

-

IP cores for ultra-low power AI-enabled devices

- Ultra-fast Response Time

- Zero-latency Switching

- Low Power

-

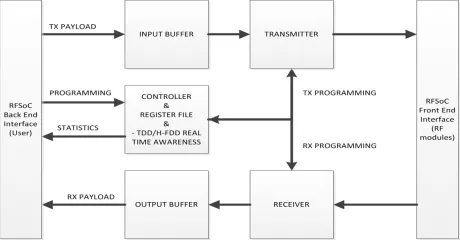

High Throughput Rate OFDM Baseband PHY Processor

- Custom OFDMA system based on 802.16e standard features.

- Complete Back-end User IF for primitive MAC integration.

-

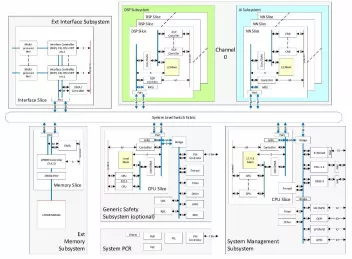

Single channel ADAS chip with FuSa monitor

- The SFA 250A has been designed to be easy to adapt to suit the support needs of the customer’s IP as it is scalable, both in terms of function and performance, as well as modular as multiple versions can be combined to form larger solutions.

-

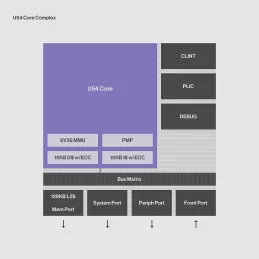

U54 Linux-capable RISC V application processor

- Fully compliant with the RISC-V ISA specification

- RV64GC U54 Application Core

- Integrated 128KB L2 Cache with ECC

- Real-time capabilities

-

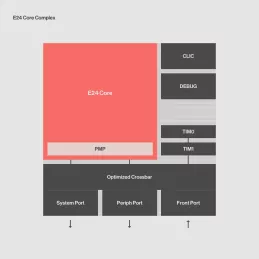

E24 High-performance microcontroller with hardware support

- RISC-V ISA - RV32IMAFC

- Machine and User Mode with 4 Region Physical Memory Protection

- 3-stage pipeline with Simultaneous Instruction and Data Access

- 2 Banks of Tightly Integrated Memory