I2C IP

Welcome to the ultimate I2C IP hub! Explore our vast directory of I2C IP

All offers in

I2C IP

Filter

Compare

101

I2C IP

from

30

vendors

(1

-

10)

-

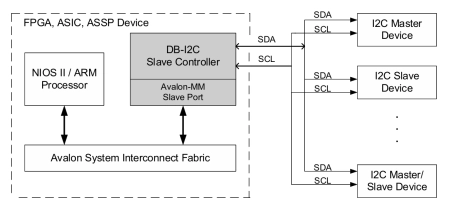

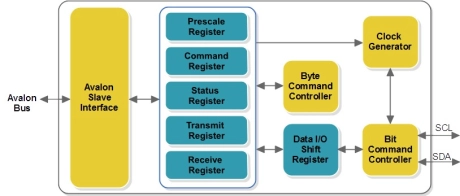

I2C Controller IP – Slave, Parameterized FIFO, Avalon Bus

- The DB-I2C-S-AHB Controller IP Core interfaces a NIOS II, ARM, MIPS, PowerPC, ARC or other high-performance microprocessor via the Avalon System Interconnect Fabric to an I2C Bus.

- The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

-

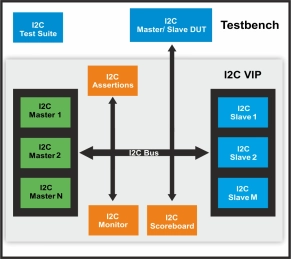

I2C/I2S/LPC Verification IP

- Fully compliant with Rev. 6 of the I2C-Bus Specification and backward compatible upto 2.1 version

- Full I2C Master and Slave functionality

- Master Transmitter/Master Receiver

- Slave Transmitter/Slave Receiver

- Master Transmitter/Master Receiver

- Slave Transmitter/Slave Receiver

-

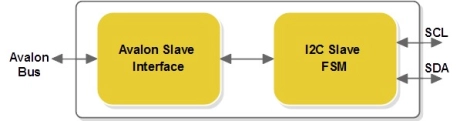

I2C Slave

- The I²C slave IP is fully synthesizable core and compatible with Phillips I²C standard. The IP uses I²C Bus Protocol which helps maximize the hardware efficiency and minimize the interfaces.

- The I²C Slave IP Core is provided as Altera SOPC Builder ready component and integrates easily into any SOPC Builder generated system.

-

I2C Master

- Avalon compliant I²C Master IP core provides an interface between Nios II processor and an I²C Slave device.

- It can work as a master transmitter or master receiver depending on working mode determined by Nios II processor.

- The I²C Master IP core incorporates all features required by the latest I²C specification including clock synchronization, arbitration, multi-master systems and fast-speed transmission mode.

-

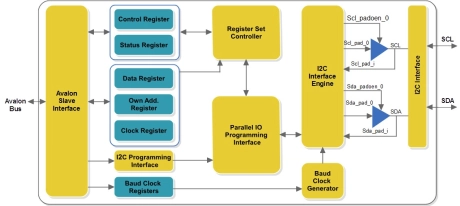

I2C Controller

- I²C (Inter-Integrated Circuit) Controller is a two-wire, bi-directional serial bus that provides simple and efficient method of data transmission over a short distance between many devices.

- Avalon compliant I²C Controller provides an interface between Nios II processor and I²C device.

- It can work as Master/Slave transmitter or Master/Slave receiver depending on working mode determined by Nios II processor.

-

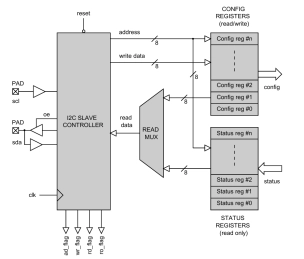

I2C Slave Serial Interface Controller

- The I2C_SLAVE IP Core is a Philips® I2C compliant slave interface controller.

- The controller decodes the SCL and SDA bus signals and converts them into a simple series of 8-bit read/write commands for accessing a set of user-defined registers.

- These registers are defined as either configuration registers or status registers.

-

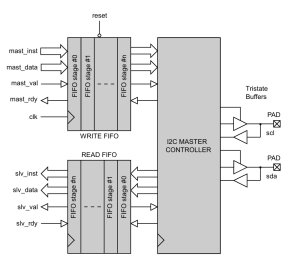

I2C Master Serial Interface Controller

- The I2C_MASTER IP Core is a Philips® I2C compliant serial interface controller capable of driving a standard two-wire bus in single-master mode.

- The controller receives data and instructions via the master instruction interface.

- These instructions are then processed by the controller state-machine in order to generate the appropriate responses on the SCL and SDA lines.

-

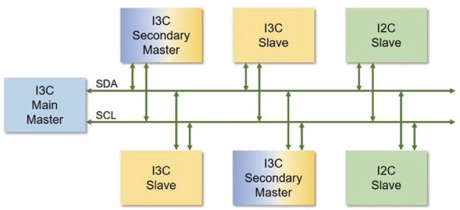

Verification IP for I3C/I2C

- A comprehensive memory VIP solution portfolio for I3C and I2C s used by system-on-chip (SoC) and IP designers to ensure comprehensive verification and protocol and timing compliance.

- Avery Verification IP for Control/Serial Buses implements a complete set of models, protocol checkers and compliance testsuite in 100% native SystemVerilog and UVM.

-

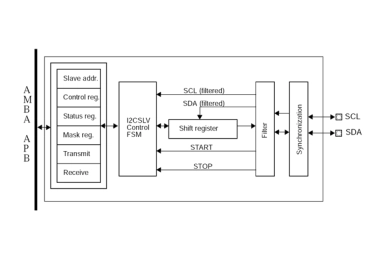

I²C Slave

- The I²C slave core is a simple I²C slave that provides a link between the I²C bus and the AMBA APB.

- The core is compatible with the Philips I²C standard and supports 7- and 10-bit addressing with an optionally software programmable address.

- Standard-mode (100 kb/s) and Fast-mode (400 kb/s) operation are supported directly.

-

I²C Master

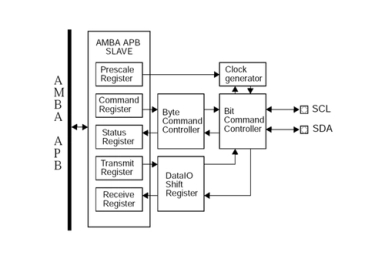

- The I²C master core is a simple I²C master that provides a link between the I²C bus and the AMBA APB.

- The I²C-master core is a modified version of the OpenCores I²C-Master where the WISHBONE interface has been replaced with an AMBA APB interface.

- The core is compatible with Philips I²C standard and supports 7- and 10-bit addressing. Standard-mode (100 kb/s) and Fast-mode (400 kb/s) operation are supported directly.