Receiver/Transmitter IP

Welcome to the ultimate Receiver/Transmitter IP hub! Explore our vast directory of Receiver/Transmitter IP

All offers in

Receiver/Transmitter IP

Filter

Compare

78

Receiver/Transmitter IP

from

32

vendors

(1

-

10)

-

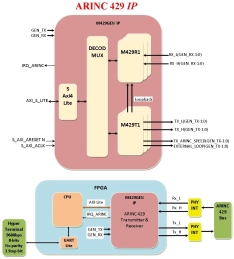

ARINC 429 IP

- The M429GEN IP implements a synchronous single-chip ARINC 429 Transmit and Receive Controller capable of linking one CPU to one or several ARINC 429 bus.

- The IP controls all ARINC 429 bus specific sequences, protocol and timing. The M429GEN IP interface allows the parallel-bus microprocessor to communicate bidirectionally with the ARINC 429 bus.

-

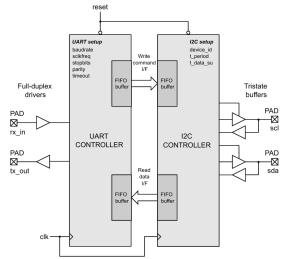

UART to I2C Bridge Controller

- The BRIDGE_UART_I2C IP Core provides a simple and convenient way to interface a standard UART bus to a standard I2C bus.

- The circuit operates as a completely transparent ‘bridge’ between the two buses and allows I2C peripherals to be programmed using a set of basic commands over a (UART) serial interface.

-

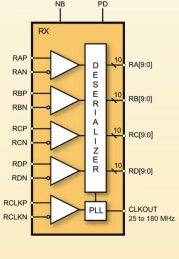

LVDS Deserializer IP

- The MXL-DS-LVDS is a high performance 4-channel LVDS Deserializer implemented using digital CMOS technology.

- Both the serial and parallel data are organized into four channels. The parallel data can be 7 or 10 bits wide per channel. The input clock is 25MHz to 165MHz. The De-serializer is highly integrated and requires no external components.

-

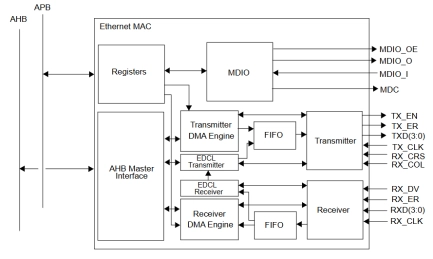

10/100 Mbit Ethernet MAC

- The GRETH core implements a 10/100 Mbit/s Ethernet Media Access Controller (MAC) with AMBA host interface.

- The core implements the 802.3-2002 Ethernet standard. Receive and transmit data is autonomously transferred between the Ethernet MAC and the AMBA AHB bus using DMA transfers.

-

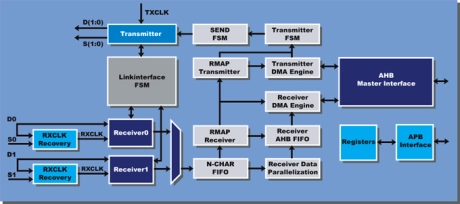

SpaceWire link controller with SpaceWire RMAP support and AMBA host interface

- Full implementation of Spacewire standard

- Protocol ID extension ECSS-E-50-12 part 2

- Optional RMAP protocol draft C

- AMBA AHB back-end with DMA

-

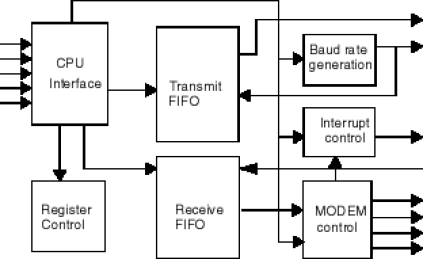

UART

- Functionally compatible with 16550.

- Supports Character (16450) and FIFO (16550) mode operations.

- Designed optimized for ASIC and PLD implementations.

- Synchronous design with edge triggered flip-flops based on system clock input.

-

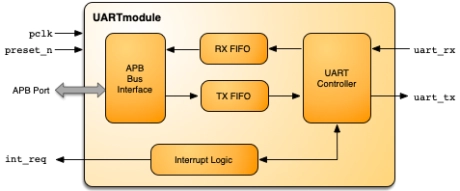

Universal Asynchronous Receiver/Transmitter Module

- The UARTmodule is part of Inicore's IPmodule family. Universal asynchronous receiver and transmitter, using the RS232 protocol, are often used to connect peripheral devices to a central controller.

- The UARTmodule has one receive and one transmit channel, receive and transmit buffers, an interrupt controller as well as a local bus interface.

-

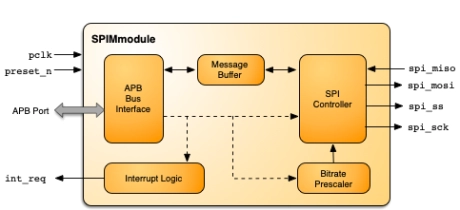

Serial Peripheral Interface (SPI) Master Module

- The SPIMmodule is part of Inicore's IPmodule family. The serial peripheral interface (SPI) protocol is often used to connect peripheral devices to a CPU.

- Several slave devices can be connected to the same bus. Since it is a serial bus, the pin count is low.

-

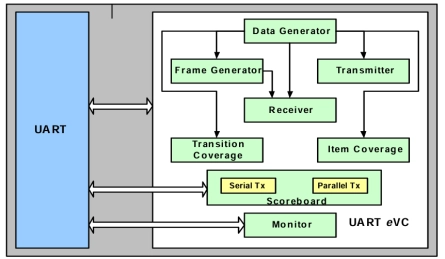

UART eVC

- UART eVC is a fully documented, off the shelf component for Cadence Specman Elite functional verification environment. At the heart of every asynchronous serial system is the Universal Asynchronous Receiver/Transmitter (UART).

- The UART is responsible for implementing the asynchronous communication process as both a transmitter and a receiver (both encoding and decoding data frames). The UART not only controls the transfer of data, but the speed at which communication takes place.

-

8530 - Serial Communication Controller

- Product Features

- Synchronous / Isosynchronous data rates

- Asynchronous capabilities

- Synchronous capabilities