Chiplet and D2D IP

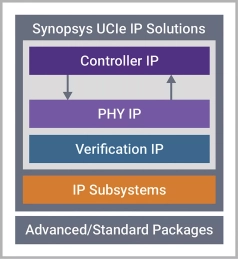

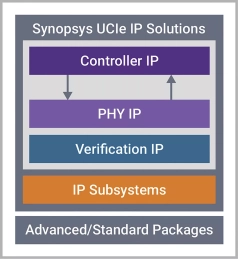

Chiplet and D2D (Die-to-Die) IP cores enable the integration of multiple chips or dies into a single system for improved performance, scalability, and efficiency. These IP cores facilitate seamless communication between individual chips, optimizing interconnects and reducing latency. Bunch of Wires IP ensures high-bandwidth, reliable connections between chips, while UCIe IP (Universal Chiplet Interconnect Express) provides a standardized interface for connecting chiplets, enabling flexible and modular chip designs. Additionally, Ultralink IP offers high-speed, low-latency communication for die-to-die interfaces, ensuring efficient data transfer across multiple processing units.

All offers in

Chiplet and D2D IP

Filter

Compare

94

Chiplet and D2D IP

from

23

vendors

(1

-

10)

-

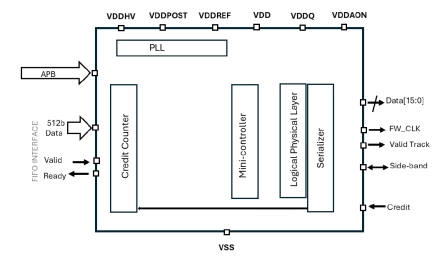

UCIe TX Interface

- Transmit-only UCIe REV1.1 with FIFO Interface

- TSMC 16FFC process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

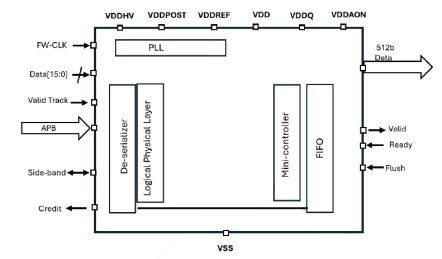

UCIe RX Interface

- Receive-only UCIe Rev1.1 with FIFO Interface

- Samsung 8nm process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

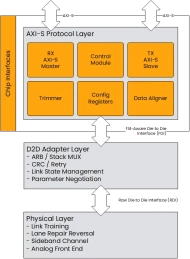

AXI-S Protocol Layer for UCIe

- Configurable Data width

- AXI4 Stream and AXI5 Stream Compliant

- All handshaking features including wakeup

- strb and keep for data flagging

-

Intra-panel TX PHY IP

- The Intra-panel TX PHY IP is a low-power transmitter designed for COG (Chip-on-Glass) and COF (Chip-on-Film) display modules.

- It supports data rates up to 4.0Gbps, utilizing a DC-coupled differential pair and a push-pull current mode driver with 600mV swing and 6dB pre-emphasis, enabling high-speed and reliable panel-to-display communication.

-

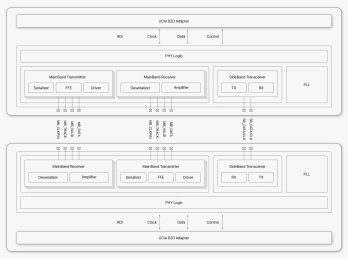

UCIe PHY (Die-to-Die) IP

- Compliant with UCIe v2.0, supporting 4/8/12/16/24/32GT/s data rates

- for Standard Package up to 16 lanes / for Advanced Package up to 64 lanes

- Provides a 1024-bit data bus width with high-throughput die-to-die communication

- Includes automatic per-lane calibration and optional transmitter de-emphasis

-

-

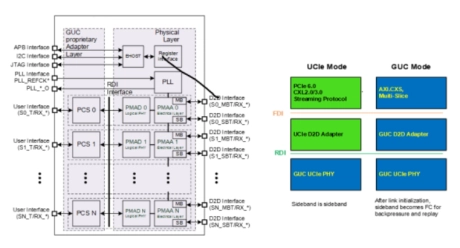

TSMC CLN5FF GUCIe LP Die-to-Die PHY

- IGAD2DY11A is an LP (Low Power) Die-to-Die (D2D) PHY for SoIC-X Face-to-Face advanced package.

- This GUCIe PHY not only supports UCIe specification rev 1.1 compliance physical layer and Raw D2D interface (RDI) but also optionally provides the

-

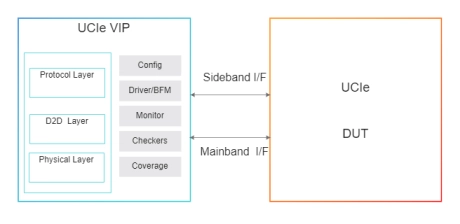

UCIe Controller baseline for Streaming Protocols for ASIL B Compliant, AEC-Q100 Grade 2

- UCIe Controller baseline for Streaming Protocols for ASIL B Compliant, AEC-Q100 Grade 2

- Low latency controller for UCIe-based multi-die designs

- Includes Die-to-Die Adapter layer and Protocol layer

-

-