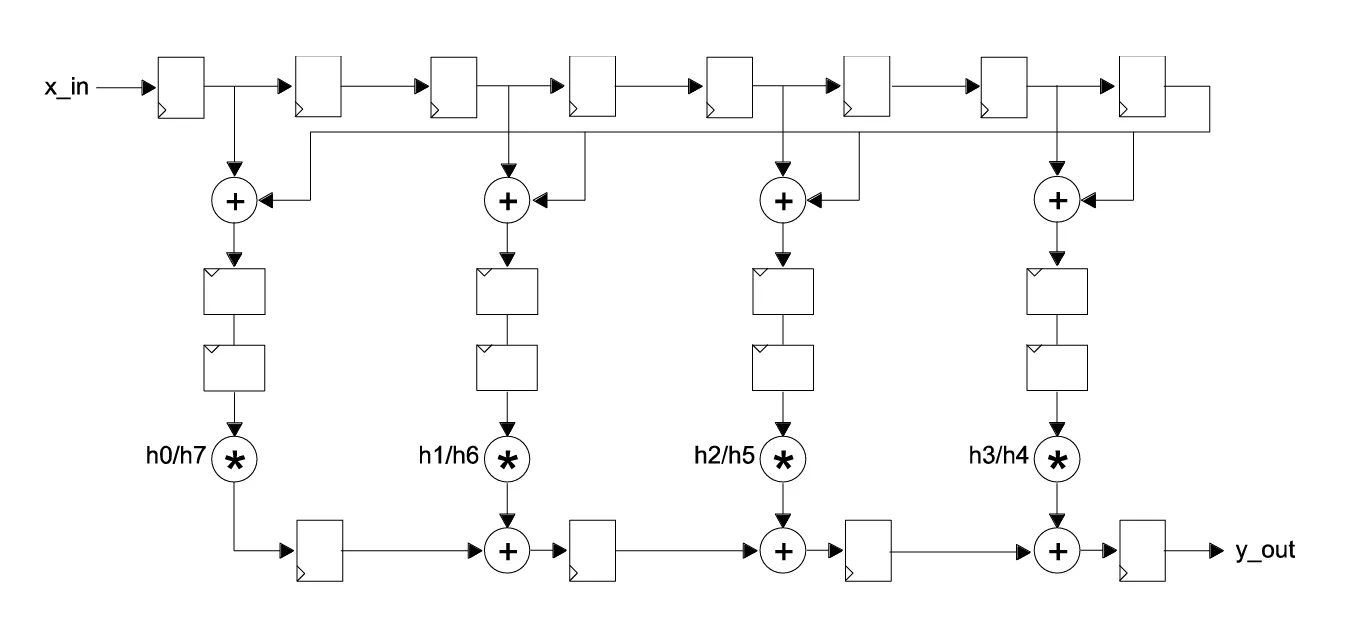

Generic high-speed FIR Filter with symmetry

FIR filter designed for high sample rate applications with symmetrical coefficients and an even or odd number of taps.

Overview

FIR filter designed for high sample rate applications with symmetrical coefficients and an even or odd number of taps. Features configurable coefficients and data width. Design uses only half the number of multipliers compared to a normal FIR implementation. Matlab®, FDAtool and Simulink® compatible.

Key features

- Synthesizable, Technology independent VHDL IP Core

- Implemented as a systolic array for speed and scalability

- 50% less multipliers than a direct-form FIR implementation

- Support for filters with inverted symmetry such as High-pass, Differentiators and Hilbert Transformers

- Configurable coefficients, data width and number of taps

- Symmetric arithmetic rounding limits DC-bias problems

- Output saturation or wrap modes

- Supports 500 MHz+ sample rates

Block Diagram

Applications

- High-speed filter applications where resources are limited

- General purpose FIR filters with symmetrical coefficients

- Filters that exhibit inverse symmetry in their coefficients such as High-pass, Differentiators and Hilbert transformers

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Filters Transforms IP core

No size fits all for signal processing on FPGA (RF Engines)

Employing general-purpose processors for radio DSP

Do's and Don'ts of Architecting the Right FPGA Solution for DSP Design

10 FPGA Design Techniques You Should Know

How to implement double-precision floating-point on FPGAs

Frequently asked questions about Filters and Transforms IP cores

What is Generic high-speed FIR Filter with symmetry?

Generic high-speed FIR Filter with symmetry is a Filters Transforms IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Filters Transforms?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Filters Transforms IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.