UCIe IP

UCIe IP Cores (Universal Chiplet Interconnect Express) facilitate high-bandwidth communication between heterogeneous chiplets, in a single package.

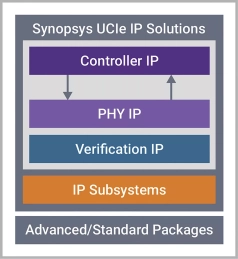

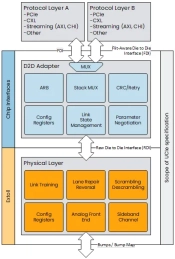

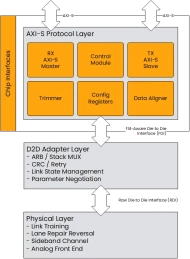

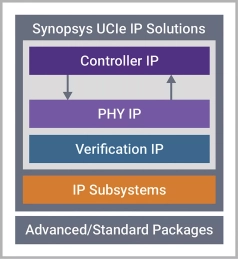

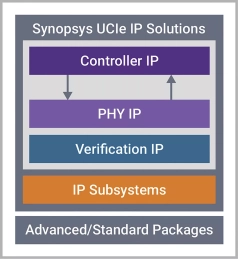

The UCIe™ physical layer includes the link initialization, training, power management states, lane mapping, lane reversal, and scrambling. The UCIe™ controller includes the die-to-die adapter layer and the protocol layer. The adapter layer ensures reliable transfer through link state management and parameter negotiation of the protocol and flit formats. The UCIe™ architecture supports multiple standard protocols such as PCIe, CXL and streaming raw mode.

Explore our vast directory of UCIe IP Cores below.

All offers in

UCIe IP

Filter

Compare

60

UCIe IP

from

22

vendors

(1

-

10)

-

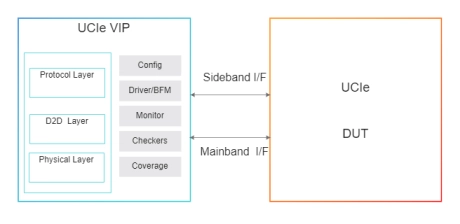

UCIe D2D Adapter & PHY Integrated IP

- The D2D Adapter for UCIe combined with the UCIe PHY from a complete UCIe solution ready to support any protocol layer.

- The offering consists of two IP parts the D2D adapter from Chip Interfaces and the UCIe PHY from Extoll.

- Chip Interfaces and Extoll collaborate on UCIe technology to create a complete solution for our customers.

-

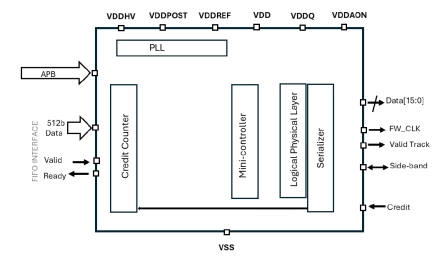

UCIe TX Interface

- Transmit-only UCIe REV1.1 with FIFO Interface

- TSMC 16FFC process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

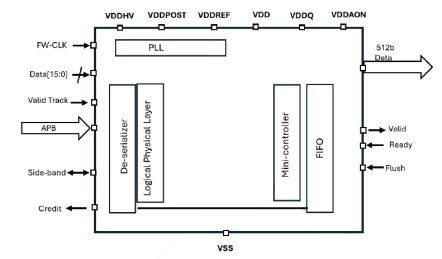

UCIe RX Interface

- Receive-only UCIe Rev1.1 with FIFO Interface

- Samsung 8nm process

- Low power UCIe D2D

- 1 pJ/bit at 0.7V

-

AXI-S Protocol Layer for UCIe

- Configurable Data width

- AXI4 Stream and AXI5 Stream Compliant

- All handshaking features including wakeup

- strb and keep for data flagging

-

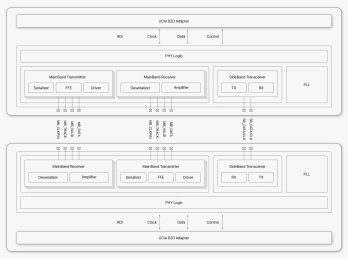

UCIe PHY (Die-to-Die) IP

- Compliant with UCIe v2.0, supporting 4/8/12/16/24/32GT/s data rates

- for Standard Package up to 16 lanes / for Advanced Package up to 64 lanes

- Provides a 1024-bit data bus width with high-throughput die-to-die communication

- Includes automatic per-lane calibration and optional transmitter de-emphasis

-

-

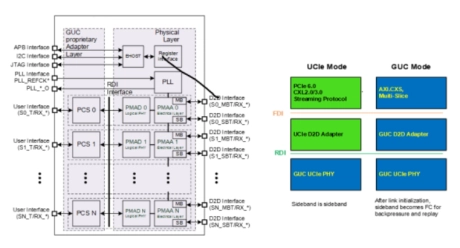

TSMC CLN5FF GUCIe LP Die-to-Die PHY

- IGAD2DY11A is an LP (Low Power) Die-to-Die (D2D) PHY for SoIC-X Face-to-Face advanced package.

- This GUCIe PHY not only supports UCIe specification rev 1.1 compliance physical layer and Raw D2D interface (RDI) but also optionally provides the

-

UCIe Controller baseline for Streaming Protocols for ASIL B Compliant, AEC-Q100 Grade 2

- UCIe Controller baseline for Streaming Protocols for ASIL B Compliant, AEC-Q100 Grade 2

- Low latency controller for UCIe-based multi-die designs

- Includes Die-to-Die Adapter layer and Protocol layer

-

-