Network-on-Chip (NoC) IP

Networks-on-Chip (NoC) are advanced communication architectures designed to facilitate efficient data transfer within complex Systems-on-Chip (SoCs). By connecting multiple cores, memory modules, and other components, NoC technology provides scalable, high-performance solutions that improve bandwidth, reduce latency, and optimize power consumption. Ideal for applications in high-performance computing, AI, IoT, and mobile devices, Networks-on-Chip ensure seamless communication in modern multi-core systems.

All offers in

Network-on-Chip (NoC) IP

Filter

Compare

25

Network-on-Chip (NoC) IP

from

14

vendors

(1

-

10)

-

NoC System IP

- Packetization allows a reduction of the wire count

- Significant reduction of the complexity of large crossbars by partitioning them into smaller ones

- Introduction of pipelining to links with heavy loads, allowing the NoC to operate faster

-

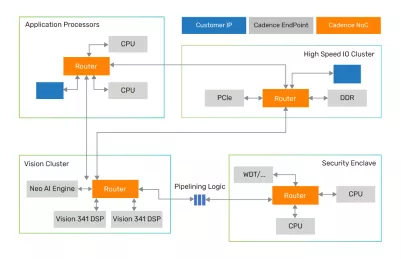

Network-on-Chip (NoC)

- InfiniNoC is a highly customizable Network-on-Chip (NoC) from InfiniNode Technologies, designed to provide a scalable, high-performance communication backbone for next-generation SoCs.

- It enables seamless integration of diverse IP blocks while delivering the flexibility, scalability, and performance required to accelerate complex chip development.

- The architecture supports high bandwidth and low latency alongside energy-efficient data movement, and it can be customized to match specific use cases and requirements.

-

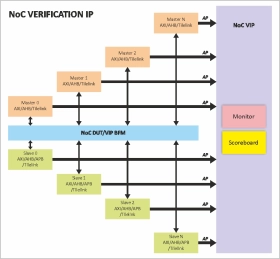

NoC Verification IP

- Complex network with acyclic agent graph (DAG). Layered and parallel NOC is also supported.

- Any number of master and slave ports is supported. Each port can be configured individually.

- ARM® AHB3-Lite,5, ARM® AXI 3,4,4-Lite,5,5-Lite, ARM® APB 2,3,4,5, SiFive TileLink Tl-UL, Tl-UH, TL-C.

-

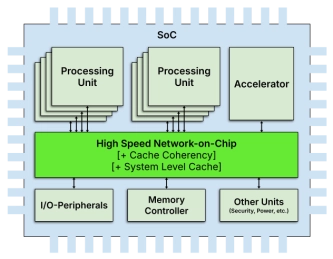

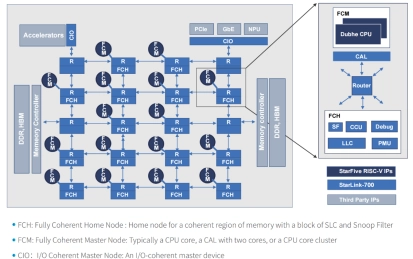

High-scalable, high-performance Interconnect fabric IP with cache coherence support

- High bandwidth, low power consumption, low latency

- Support Component Aggregation Layer (CAL)

- Topology: Mesh

- Support multiple I/O Coherent Master Nodes (CIO)

- Maximum node count: 12x12

-

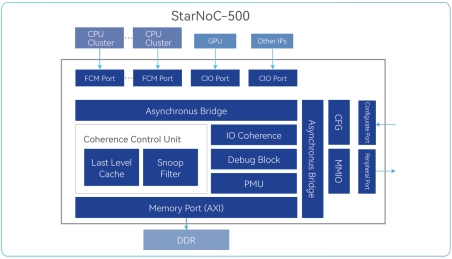

Interconnect fabric IP with cache coherence support

- StarNoC-500 is the vendor's first self-developed interconnect fabric IP with cache coherence support, supporting the construction of multi-cores and SoC.

-

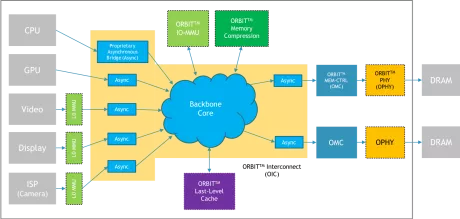

High speed NoC (Network On-Chip) Interconnect IP

- The ORBIT On-Chip Interconnect (OIC) delivers exceptional performance, and SoC design flexibility based on automated end-to-end interconnect generation flow.

- It enables high-speed routing with pre-calculated routing path details and supports higher speed, low latency, and floorplan flexibility.

-

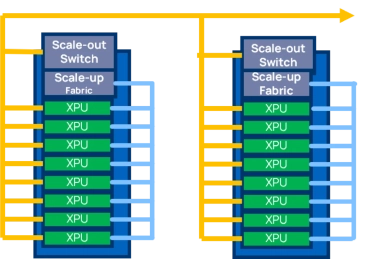

Scalable Switch Fabric

- The NeuraScale Scalable Switch Fabric is a WeaveIP™ advanced system IP solution that is designed from the ground-up to provide non-blocking switching between a large number of UALink™, Ultra Ethernet, or AMBA ports for the emerging scale-up and scale-out systems.

- Extreme port density is achieved while maintaining near lowest theoretical latency, tight latency-bandwidth curve and simple physical design with design tiles.

-

Smart Network-on-Chip (NoC) IP

- Smart NoC automation

- Topology generation with minimum wire length

- Scripting-driven regular topology creation

- Incremental design capability

- Auto-timing closure assist

-

-

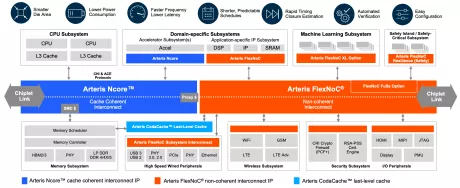

FlexNoC 5 Option For Scalability and Performance Critical Systems

- Scales from 10s to 100s of IP blocks

- Automatically generates ring, mesh and torus networks

- View and edit generated topologies