IP stack IP

Welcome to the ultimate IP stack IP hub! Explore our vast directory of IP stack IP

All offers in

IP stack IP

Filter

Compare

60

IP stack IP

from

19

vendors

(1

-

10)

-

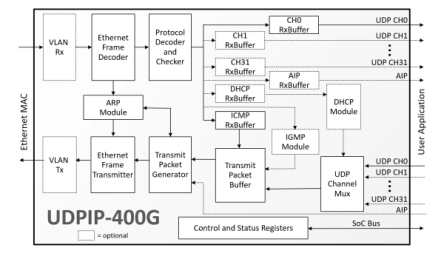

400G UDP/IP Hardware Protocol Stack

- Implements a UDP/IP hardware protocol stack that enables high-speed communication over a LAN or a point-to-point connection.

- Designed for standalone operation, the core is ideal for offloading the host processor from the demanding task of UDP/IP encapsulation and enables media and data streaming with speeds up to 400Gbps in ASICs even in processor-less SoC designs.

-

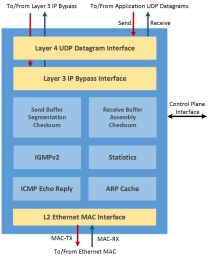

UDP Offload Engine for IPv4

- The UDP/IP core implements the UDP/IPv4 standard RFC 768/791, including checksum, segmentation and reassembly hardware offload.

- The UDP/IP core is tested for operation with popular FPGA vendors’ GbE Ethernet MACs.

-

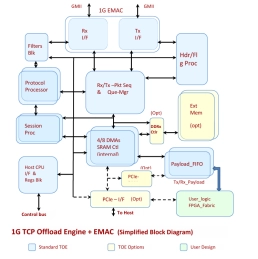

1G TCP Offload Engine TOE Very Low Latency (TOE)

- Ideal for high performance and mid performance specialized, differentiable ASICs or FPGAs for Network security or Network infrastructure applications

- Less than 4000 Xilinx slices, Altera ALMs or 150,000 ASIC gates + on-chip memory

- Fully integrated 100 M bit/1-G bit high performance EMAC.

- Scalable MAC Rx FIFOs and Tx FIFOs make it ideal for optimizing system performance.

-

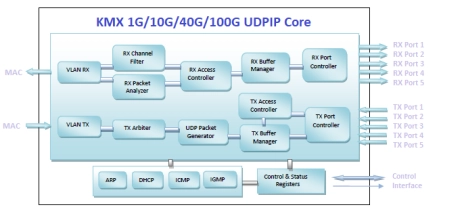

100G UDP/IP Hardware Protocol Stack Core

- The core Implements a UDP/IP hardware protocol stack that enables high-speed communication over a LAN or a point-to-point connection.

- It is ideal to offload systems from demanding tasks of UDP/IP and to enable media streaming in both FPGA and RISC designs.

- The core supports ARP request, reply and manages 32-entry ARP cache. ICMP ping reply is included.

-

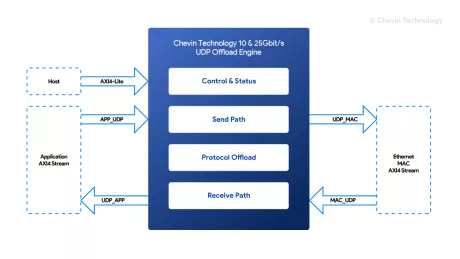

UDP/IP Offload Engine - 10G/25G/40G/100Gbit/s Ethernet UDP/IP

- AXI4s MAC & Application Interfaces

- De-fragmentation option available

- Designed to UDP specification RFC768

- Compose/Decompose complete UDP Datagrams

-

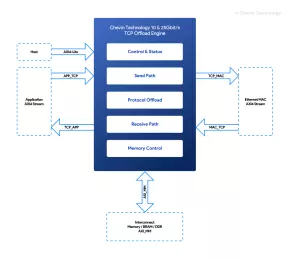

TCP/IP Offload Engine - 10G/ 25G/40G/100Gbit/s TCP/IP

- 1 to 256 Simultaneous connections

- Server/Client roles, configurable per connection

- Automatically establish & tear-down connections

- All-RTL send/receive for extremely low latency

-

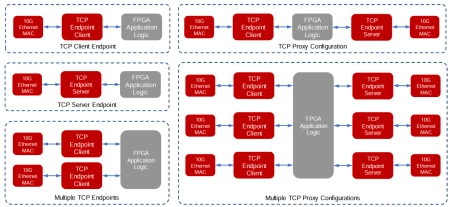

Ultra Low Latency 10G TCP Endpoint

- The TCP Endpoint implements a full, reliable streaming network stack in FPGA logic.

- It allows applications in logic to be directly connected to Internet Protocol (IP) interfaces by opening, maintaining, and closing TCP Connections via Ethernet to other hardware or software endpoints.

-

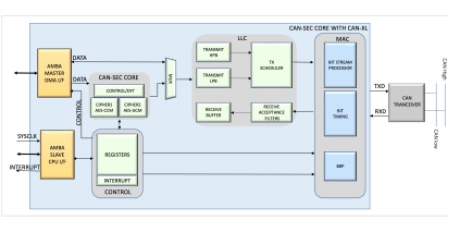

CAN-SEC Bus Controller IP

- The CAN-SEC Acceleration Engine Core implements the CAN-XL Protocol (CiA 610-1), CAN-XL Addon Part 1-Simple/Extercontent Indication (CiA 613-1), and CAN-XL Addon Part 2-Security (CiA 613- 2) Protocols.

- The CAN-SEC Acceleration Engine core is easy to integrate with the Host processor using AMBA-APB, AHB_Lite or AMBA-AXI standard interface.

-

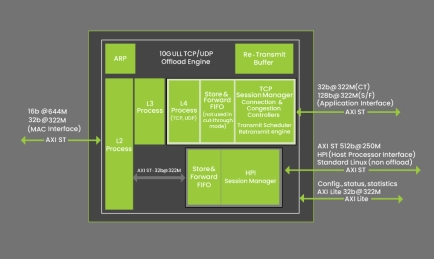

ULL TCP/IP, UDP/IP Offload Engine

- High-performance TCP and UDP IP offload engine cores offer a reliable, ultra-low-latency solution for financial and network applications.

- They address the data center industry’s growing need for throughput and hardware acceleration and provide network protocol offload for applications such as financial data processing, reprogrammable Smart NICs, and high-performance computing.

-

100G UDP Offload Engine - Offloads UDP packet processing for efficient, high-speed networking

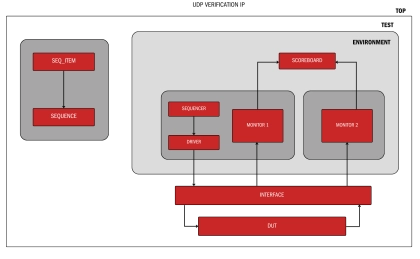

- The 100G UDP Offload Engine in Verification IP (VIP) offloads UDP packet processing to specialized hardware, enhancing data transmission efficiency. It ensures low latency and high throughput with support for checksum offloading, segmentation, and reassembly.

- This solution is ideal for high-speed networks, including data centers, telecoms, and multimedia streaming. It supports both IPv4 and IPv6 protocols, delivering optimized performance for real-time applications, from gaming to AI/ML data transmission.