Ethernet IP

Ethernet IP cores, including 112G and 224G PHYs, up to 1.6T controllers, MACsec security modules, and Verification IP, offer optimized power, performance, area, and latency for automotive, HPC, AI, and IoT SoCs.

Ethernet is defined in a number of IEEE 802.3 standards. These standards define the physical and data-link layer specifications for Ethernet.

Explore our vast directory of Ethernet IP cores below

All offers in

Ethernet IP

Filter

Compare

383

Ethernet IP

from

67

vendors

(1

-

10)

-

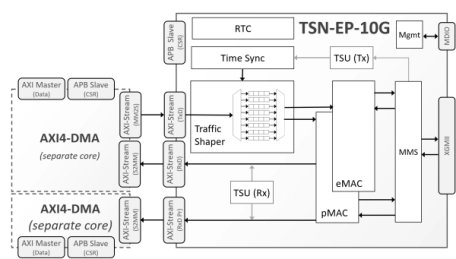

TSN Ethernet Endpoint Controller 10Gbps

- The TSN-EP-10G implements a configurable controller meant to ease the implementation of endpoints for networks complying with the Time Sensitive Networking (TSN) standards

- It integrates hardware stacks for timing synchronization (IEEE 802.1AS-2020) and traffic shaping (IEEE 802.1Qav and 802.1Qbv), frame-preemption (IEEE 802.1Qbu and IEEE 802.3br) and a low-latency Ethernet MAC.

-

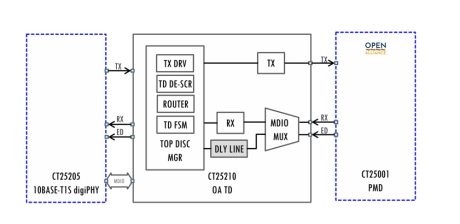

OPEN Alliance TC14 10BASE-T1S Topology Discovery IP

- The CT25210 Topology Discovery (TD) IP coordinates all operations required to perform 10BASE-T1S topology discovery measurements. It integrates several functional blocks, each responsible for a specific phase of configuration, training, measurement, and signal handling within the discovery process.

- At the top level, the TD Manager supervises the measurement flow and configuration setup. Within this block, the TD Mode Manager manages the receive-only operating mode and distributes the necessary clock signals to other TD modules.

-

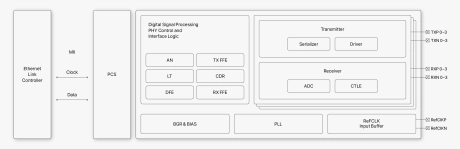

Ethernet PHY IP

- Compliant to 802.3 Ethernet specification - 200GBASE-KR4, 200GBASE-CR4, 100GBASE-KR4, 100GBASE-CR4, 100GBASE-KR2, 100GBASE-CR2, 50GBASE-KR, 50GBASE-CR, 40GBASE-KR4, 40GBASE-CR4, 25GBASE-KR, 25GBASE-CR, 10GBASE-KR, 10GBASE-CR

- Data rate supported - Ethernet: NRZ 3.125 - 26.5625Gb/s, PAM4 53.125Gb/s

- DSP-based architecture using high-performance ADC/DAC for RX/TX

-

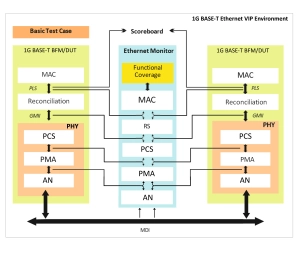

1G BASE-T Ethernet Verification IP

- The 1G BASE-T Ethernet Verification IP provides deliverables an effective & efficient way to verify the components interfacing with the Ethernet interface of an IP or SoC.

- The 1G Ethernet VIP is fully compliant with the IEEE standard 802.3 specification.

- This VIP is lightweight with easy plug -and- play interface so that there is no hit on the design cycle time.

-

Simulation VIP for Ethernet UEC

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Callbacks access at multiple TX and RX queue points for scoreboarding, data manipulation, and error injection

- Transaction Tracker: Configurable tracking of all the transactions on the channels

-

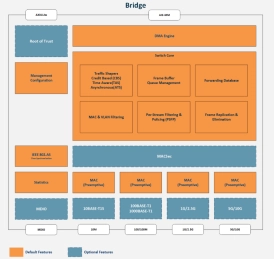

Bridge

- A complete integrated hardware and software solution that includes a TSN-capable Ethernet switch, a DMA engine, an IEEE 802.1 AS Time Synchronization system, and a Root of Trust security module.

-

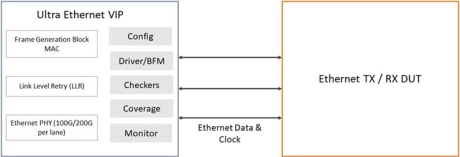

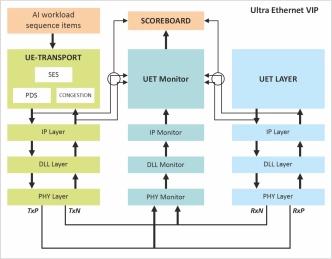

Ultra Ethernet Verification IP

- The Ultra Ethernet (UE) Verification IP provides an effective & efficient way to verify the components interfacing with Ethernet interface of an IP or SoC.

- The UE VIP is compliant with IEEE standard 802.3-2018 & UE Specifications V1.0.

- This VIP is light weight with easy plug-and-play interface so that there is no hit on the design cycle time.

-

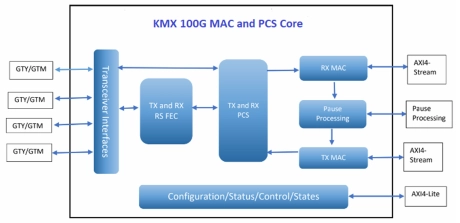

100G MAC and PCS core

- KMX 100G MAC and PCS core, which consists of media access control (MAC) module, physical coding sublayer (PCS) module and physical medium attachment (PMA) module, is compliant with the IEEE 802.3ba-2010 standard.

- The core implements RS FEC as defined in IEEE 802.3bj Clause 91 with independent bit error detection and bit error correction.

-

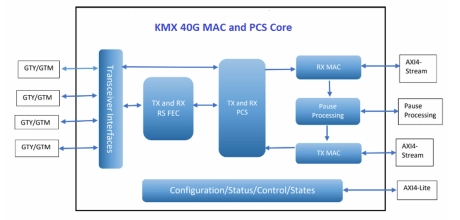

40G MAC and PCS core

- KMX 40G MAC and PCS core, which including media access control (MAC) module, physical coding sublayer (PCS) module and physical medium attachment (PMA) module, is compliant with the IEEE 802.3ba-2010 standard.

- The core supports RS FEC as defined in Clause 74 IEEE 802.3 with independent error bit detection and error bit correction.

-

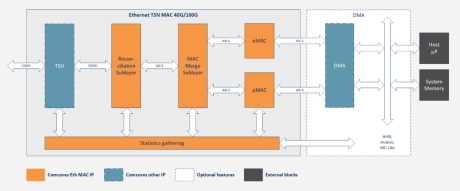

Ethernet TSN MAC 40G/100G

- Silicon agnostic Ethernet TSN MAC IP with speeds of 40G and 100G, based IEEE 802.3 Ethernet Layer 2 solution with support for key TSN features