Multimedia IP

Multimedia IP cores are IP blocks used in the design of multimedia processing systems. These IP cores are typically developed to perform specific functions related to handling multimedia data, such as audio, video, graphics, and imaging. Multimedia IP cores can handle a variety of tasks, including:

- Video Encoding/Decoding (Codec): IP cores that can compress or decompress video streams (e.g., H.264, HEVC, VP9).

- Audio Encoding/Decoding: IP cores used to compress or decompress audio data (e.g., MP3, AAC).

- Image Processing: IP cores for tasks like scaling, filtering, or converting images (e.g., resizing, color space conversion).

- Graphics Processing: IP cores for rendering graphics, handling 2D or 3D graphics rendering, and processing graphic objects in video games, GUIs, or other visual applications.

- Video Streaming: IP cores that manage real-time streaming of video data for playback or transmission.

- Signal Processing: IP cores that process signals from sensors, cameras, microphones, etc., typically to filter, enhance, or interpret the data.

All offers in

Multimedia IP

Filter

Compare

591

Multimedia IP

from

82

vendors

(1

-

10)

-

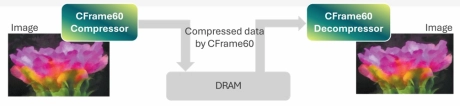

Lossless & Lossy Frame Compression IP

- Supports Lossless/Lossy.

- Lossy compression ratio : 1/2~1/4.

- Rate control : Image complexity detection (Lossy only).

- Input order : Picture raster-scan order, and tile raster-scan order.

-

-

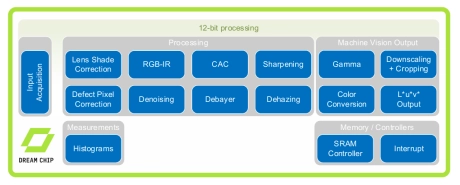

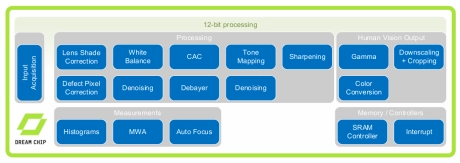

Real-time Pixel Processor for Vision applications

- The W Series provides configurable input and output data widths.

- It supports input image frames with 8 to 16-bit amplitude resolutions, while it can output tone-mapped frames with 12 bits per pixel.

- The W Series are ISPs which are optimized for area while getting the best image quality.

-

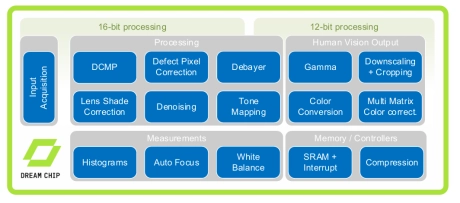

Real-time Pixel Processor for Vision applications

- The H Series provides configurable input and output data widths. It accepts YCbCr or RAW input data and supports input image frames with 8, 10 and 12-bit amplitude resolutions.

- The H1 Series are ISPs which are optimized for area while getting the best image quality.

- Options to extend the pipeline with a Machine Vision output or configuring the line size to further optimize area are possible.

-

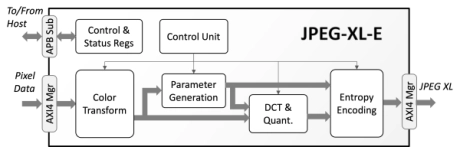

JPEG XL Encoder

- The JPEG-XL-E implements an image compression engine compliant to the JPEG XL, ISO/IEC 18181 standard.

- Leveraging the advanced coding tools of the JPEG XL standard, the core achieves substantially higher compression efficiency than legacy JPEG while requiring fewer hardware resources than JPEG 2000 and comparable codecs.

-

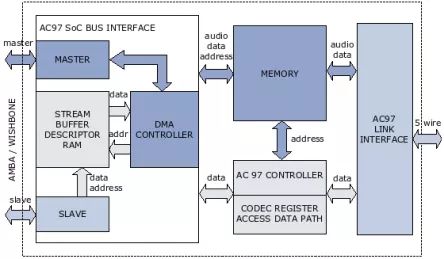

AC97 Audio Controller

- Fixed 48kHz audio support

- Hardware variable sample rate support from 8kHz to 48kHz (up to 96kHz with Double Rate Audio enabled)

- Double Rate Audio support for Left, Right and Center channels

- 16 bit sample size support (18 and 20 bit support planned in future)

-

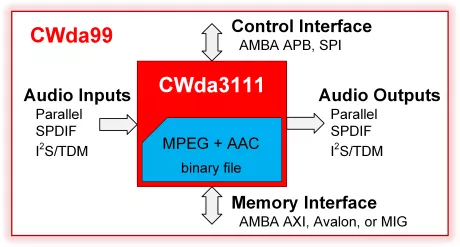

MPEG-1/2 + AAC Audio Decoder

- The MPEG-1/2+AAC Audio Decoder (CWda99) is an audio IP core for decoding up to 6 audio channels in real-time.

- This core contains the MPEG + AAC decoder software and the Coreworks processor based hardware audio engine platform (CWda3111).

-

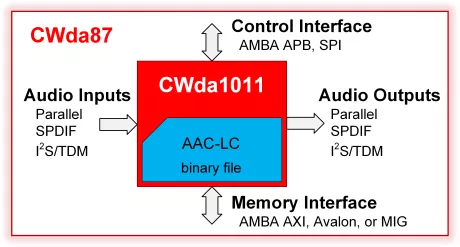

AAC-LC Audio Decoder

- The AAC-LC Audio Decoder (CWda87) is an audio IP core for decoding up to 6 audio channels in real-time.

- This core contains the AAC-LC decoder software and the Coreworks processor based hardware audio engine platform (CWda1011).

-

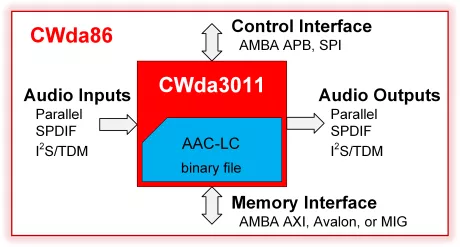

AAC-LC Audio Encoder

- The AAC-LC Audio Encoder (CWda86) is an audio IP core for encoding up to 6 audio channels in real-time.

- This core contains the AAC-LC encoder software and the Coreworks processor based hardware audio engine platform (CWda3011).

-

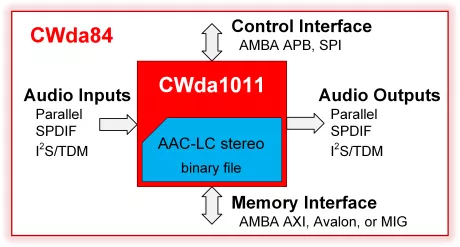

AAC-LC Stereo Audio Encoder

- The AAC-LC Stereo Audio Encoder (CWda84) is an audio IP core for encoding one stereo stream in real-time.

- This core contains the AAC-LC stereo encoder software and the Coreworks processor based hardware audio engine platform (CWda1011).