Security Processor IP

Security Processor IP cores support advanced security features such as encryption, decryption, authentication, and secure boot, safeguarding devices against cyber threats and unauthorized access. Ideal for applications in IoT, automotive, mobile devices, and financial systems, Security Processor IP cores help developers integrate trusted, high-performance security capabilities into their designs.

All offers in

Security Processor IP

Filter

Compare

16

Security Processor IP

from

7

vendors

(1

-

10)

-

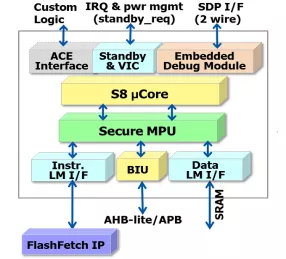

Compact Processor for Security

- Secure MPU against memory tampering

- Shields against side-channel attack

- Secure debug for multi-party software development

- Flexible configurations and run-time control

-

Secure Execution Processor

- The Geon™ Secure Execution Processor is a low-power, 32-bit processor IP core with built-in protection of sensitive code and data.

- It uses two or more cryptographically separated execution contexts for a high degree of security during code execution and for data storage and transfer to and from the processor.

-

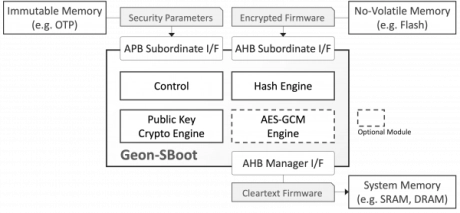

GEON™ Secure Boot Hardware Engine

- GEON-SBoot is an area-efficient, processor-agnostic hardware engine that protects SoC designs from booting with malicious or otherwise insecure code.

- The security platform employs public-key cryptography (which stores no secret on-chip) to ensure that only unmodified firmware from a trusted source is used by the system.

-

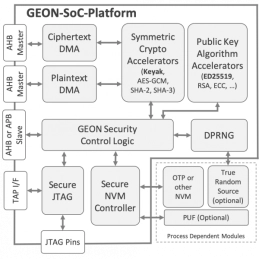

SoC Security Platform / Hardware Root of Trust

- GEON-SoC is an area-efficient, processor-agnostic, hardware root of trust for SoC designs.

- It implements secure boot and can optionally be enhanced to support firmware decryption and secure debug, or to act as a post-boot hardware security module (HSM).

-

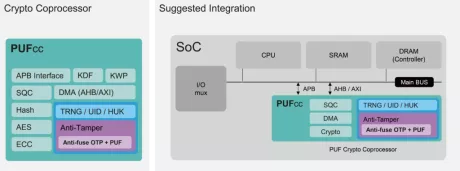

Crypto Coprocessor

- Comprehensively support all CPU architectures

- Crypto engine collective, consisting of private key cipher, message authentication code, hash, and key derivation functions that are NIST CAVP certified and OSCCA standards compliant

- Key wrapping function aiding the export of keys for external use

-

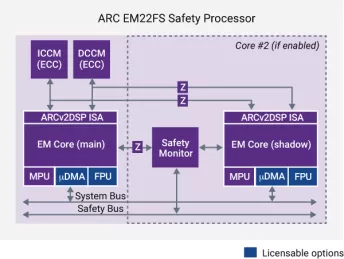

ARC EM22FS safety processor

- Dual-core lockstep safety processor supports ISO 26262 automotive safety standards

- Single solution support for safety level up to ASIL D; Supports both ASIL D lockstep operation or ASIL B single core operation

- Includes hardware safety features such as ECC, integrated user-programmable windowed watchdog timer, and lockstep safety monitor

-

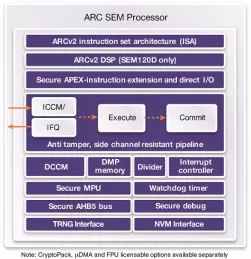

ARC SEM120D Security Processor with DSP for Low Power Embedded Applications

- Performance-, power- and area-efficient security processors for embedded applications

- Secure privilege mode orthogonal to kernel/user mode

- Enhanced secure MPU with context ID for secure or normal operation

- Up to 16 configurable protected regions and per region scrambling capability

-

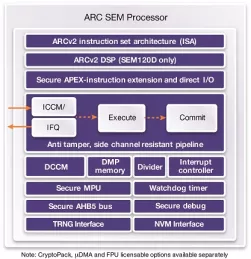

ARC SEM110 Security Processor for Low Power Embedded Applications

- Performance-, power- and area-efficient security processors for embedded applications

- Secure privilege mode orthogonal to kernel/user mode

- Enhanced secure MPU with context ID for secure or normal operation

- Up to 16 configurable protected regions and per region scrambling capability

-

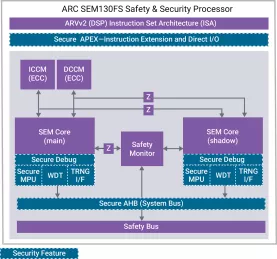

ARC SEM130FS Safety and Security Processor

- ASIL D compliant dual-core, lockstep safety processor supports ISO 26262 automotive safety standards and provides advanced security to protect against evolving threats

- Secure privilege mode orthogonal to kernel/user mode

- Integrated self-checking safety monitor capable of time diversity

- Uniform instruction timing and timing/ power randomization for side channel resistance

-

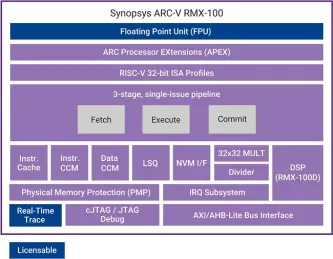

ARC-V RMX-100 Processor IP

- Family of 32-bit RISC processors for ultra-low power embedded applications

- Based on the RISC-V ISA, leveraging standard 32-bit protocols (and extensions)

- DSP instruction extensions (RMX-100D)

- Easy DSP programming support with MetaWare C/C++ Compiler (RMX-100D)