Clocking IP

All offers in

Clocking IP

Filter

Compare

2,954

Clocking IP

from

75

vendors

(1

-

10)

-

Crystal Oscillator for a 32 kHz Crystal - GLOBALFOUNDRIES® 22FDX®

- Specific crystal: 32 kHz

- Supported series resistance: up to 100 kOhm

- Supported load capacitance: 3 pF to 12.5 pF

- Startup time: 59 ms (TT, 12 pF) depending on crystal and PCB

-

Clock Buffer - X-FAB XT018-0.18µm BCD-on-SOI CMOS

- Max Load: 25pF total (including padcell and bondwire parasitics)

- Signal Integrity: Maintains tight rise/fall timing (1.4-3.1ns) across a wide load range (1pF to 26pF)

- Low Propagation Delay: 6ns typical delay at max load, ensuring fast response for real-time systems

- Efficient Power Use: 6.5mA average current at 40MHz with 25pF load, balancing performance and energy efficiency

-

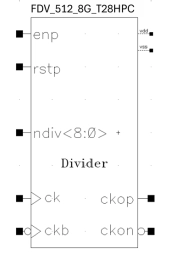

Frequency Divider

- Division ratio: any integer from 1 to 8/64/512/4096

- Maximum input frequency 2GHz – 10+GHz (A)

- Clock input and output signals are differential CMOS

- Control signals are single ended CMOS

-

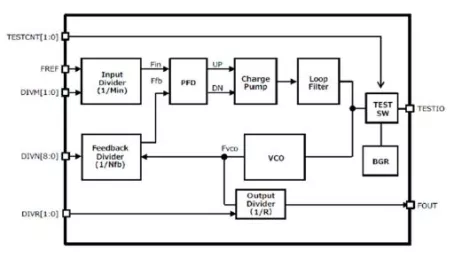

High Speed Integer PLL IP

- Up to 4Ghz clock output

- Wide range of multiplicand

- Small physical area

- TEST pin integrated

-

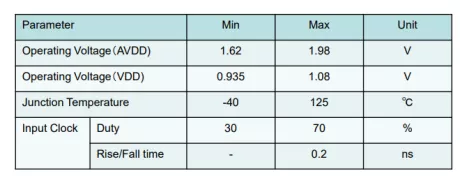

1.7GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 850MHz - 1700 MHz

- Output frequency range : 850MHz -1700 MHz

- Input frequency range : 9.6MHz - 216MHz

-

5GHz Multiplying PLL on TSMC 28nm

- Including Loop-filter

- VCO operating range : 2500MHz - 5000 MHz

- Output frequency range : 1250MHz - 2500 MHz

- Input frequency range : 12MHz - 320 MHz

-

1.8GHz SSCG PLL on TSMC 28nm HPC+

- Including Loop-filter

- VCO operating range : 900MHz - 1800 MHz

- Output frequency range : 900MHz-1800 MHz

- Input frequency range : 12MHz - 192MHz

-

3.2GHz SSCG PLL on TSMC 12nm

- Including Loop filter

- VCO operating range : 1600MHz- 3200MHz

- Output frequency range: 400MHz- 3200MHz

- Input frequency range : 10MHz- 200MHz

-

4.3GHz SSCG PLL on TSMC 7nm

- Including Loop filter

- VCO operating range : 2000MHz-4300MHz

- Output frequency range: 500MHz-4300MHz

- Input frequency range : 10MHz- 200MHz

-

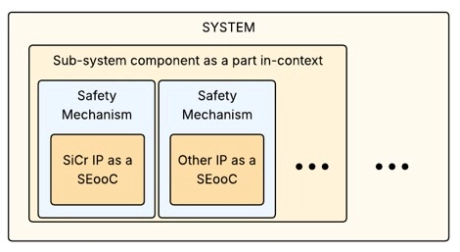

Automotive Grade PLLs, Oscillators, SerDes PMAs, LVDS/CML IP

- TSMC IP9000 Alliance member enabling automotive IP support in TSMC automotive processes

- Automotive Documentation including Safety Manual, FMEDA and DFMEA

- Design reliability report containing EM/IR and Aging analysis