IEEE 1394 (FireWire) IP

Welcome to the ultimate IEEE 1394 (FireWire) IP hub! Explore our vast directory of IEEE 1394 (FireWire) IP

All offers in

IEEE 1394 (FireWire) IP

Filter

Compare

10

IEEE 1394 (FireWire) IP

from

3

vendors

(1

-

10)

-

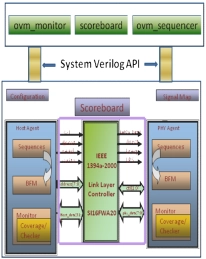

IEEE 1394 OVC

- IEEE 1394a-2000 Link Layer Controller eVC is a fully documented, off the shelf component for Cadence Specman Elite functional verification environment.

- The IEEE 1394 a-2000 link layer controller (from now on referred to only as 1394a) provides connectionless acknowledged data transfer services between a source node and destination node where node is an addressable device attached to the serial bus with at least a minimum set of control registers.

-

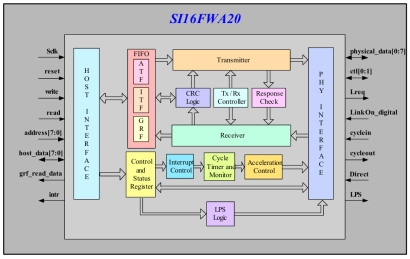

IEEE 1394a - 2000 Link Layer Controller

- The Link core is a functional block available for insertion into a customer's ASIC design, which supports the IEEE 1394a - 2000 Draft specifications for a high - speed serial bus.

- The SI16FWA20 Link core is implemented using VHDL synthesizable code to provide portability across Silicon Interfaces Gate Array and Cell - Based ASIC technologies.

-

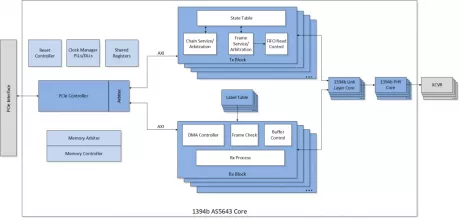

Mil1394 AS5643 Link Layer Controller IP Core

- AS5643 compliant interface with hardware based STOF offload

- Hardware DMA engines with message label mapped buffers

- STOF transmitter and receiver hardware functions

- Supports S100/S200/S400 data rates

-

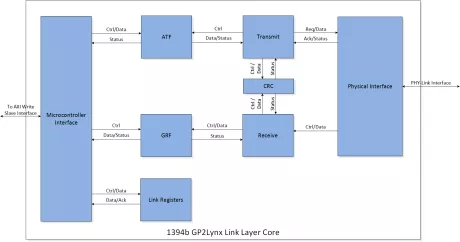

Mil1394 GP2Lynx Link Layer Controller IP Core

- AS5643 compliant interface with hardware-based STOF offload

- Supports S100/S200/S400 data rates

- Configurable number of GP2Lynx nodes in a single FPGA

- Legacy microprocessor or AXI host interface available

-

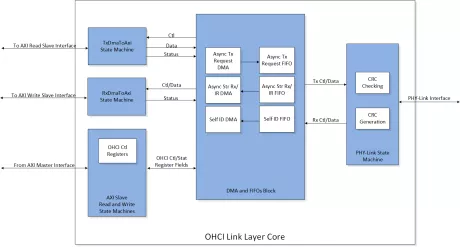

Mil1394 OHCI Link Layer Controller IP Core

- AS5643 compliant interface with hardware based STOF offload

- Supports S100/S200/S400/S800/S1600/S3200 data rates

- Configurable number of OHCI nodes in a single FPGA

- AXI-based host interface for embedded or PCIe based processors

-

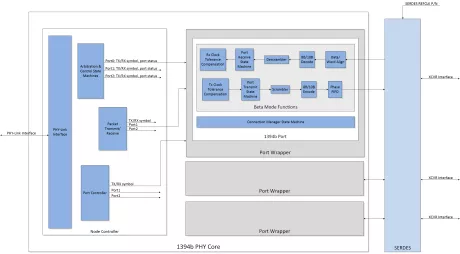

1394b PHY IP Core

- AS5643 compliant interface

- Supports S100 / S200 / S400 / S800 / S1600 / S3200 data rates

- Complete PHY layer implementation

-

FireLink IEEE1394b Link Layer Controller

- IEEE 1394-1995, 1394a-2000 and 1394b-2002 compliant

- Supports 100, 200, 400, and 800Mbps data transfer rates

- Supports Legacy and Beta packets RX/TX (depending on the connected PHY)

- Supports all standard 1394 packet types

-

1394b FPGA Link Layer Controller

- Complete IP solution combining FireLink® Basic and FireGate

- IEEE-1394-2008 Beta

- Supports S100-S3200 transfer rates

- Minimal Footprint

-

IEEE-1394b PHY layer Core

- Complete IP solution supporting IEEE-1394b-2008 and AS5643

- Support for speeds from S100 to S3200

- Single-Speed Support (S100, S200, S400, ...)

- Multi-Speed Support (S100 - S400, S800 - S3200)

-

1394B I/O

- Single-chip solution: The PHY IP can be combined with Link Layer IPs, creating smaller solutions. Additional components can be added to create a System On Chip (SOC) solution.

- Flexible number of ports: Commercially available PHY chips have a fixed number of ports which for small peripherals is often overkill. On the other hand, host adapter would likely benefit from 3 or more ports and a hub could even have more than that. For a PHY based on FPGA technology, the user can customize the number of ports as required.

- Optional debug and test features: Optionally the user can include debug and test features like BERT (Bit Error Rate Test) Low level data monitoring and recording

- Field-upgradable: The used FPGAs are field upgradable thus allowing the addition new features or bug fixes, even if the device is already in the field.