LCD Controller IP

Welcome to the ultimate LCD Controller IP hub! Explore our vast directory of LCD Controller IP

All offers in

LCD Controller IP

Filter

Compare

28

LCD Controller IP

from

9

vendors

(1

-

10)

-

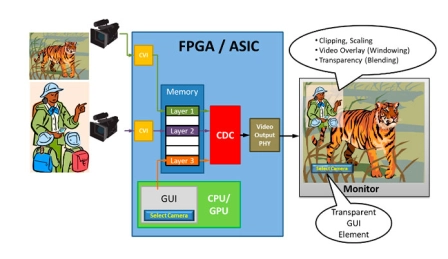

Customizable Display Controller IP

- CDC is a fully Customizable Display Controller IP supporting up to 16k resolutions (4096x4096 pixel) on a MIPI-DPI compliant parallel video output.

- Several features can be configured at synthesis time and programmed at run time.

- The display controller can be applied to e.g. FPGA systems with a resource optimized, application specific feature configuration or to ASIC projects applying a more generic feature set and thus more flexibility.

-

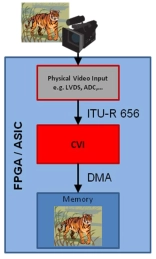

Customizable Video Input controller

- CVI is a fully Customizable Video Input controller IP core.

- The video input controller can be applied to e.g. FPGA systems with a resource optimized, application specific feature configuration or to ASIC projects applying a more generic feature set and thus more flexibility.

-

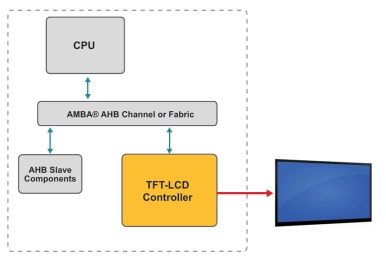

AHB TFT LCD Controller w/ DMA

- The AHB TFT LCD Controller is a configurable core that interfaces to an AHB microprocessor bus and provides all the timing control and pixel serialization for controlling various TFT LCD Display Panels.

- The core can also be used with various RAMDACs to interface to VGA Monitors or VGA style LCD Panels.

- The AHB TFT LCD Controller supports 24-bit true color and 16-bit color, as well as an 8-bit color display mode via the 256 Pixel Palette Ram.

-

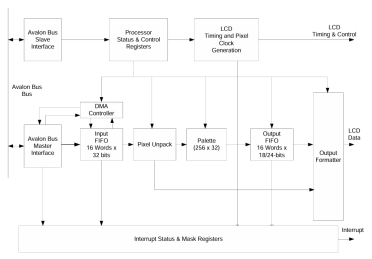

Display Controller – LCD / OLED Panels (Avalon Bus)

- The DB9000AVLN TFT LCD Controller IP Core interfaces a microprocessor and frame buffer memory via the Avalon Bus within Altera Qsys Integration (generating the System Interconnect Fabric) to a TFT LCD panel.

- In an Altera FPGA, typically, the microprocessor is a NIOS II or ARM processor and frame buffer memory is either on-chip SRAM memory or larger off-chip SRAM or SDRAM.

-

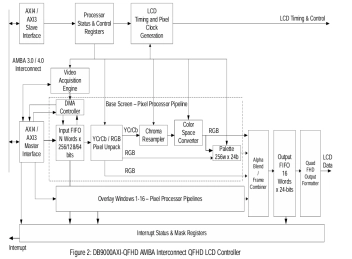

Display Controller – Ultra HD LCD / OLED Panels (AXI4/AXI Bus)

- The DB9000AXI4-UHD LCD Controller IP Core interfaces a video image in frame buffer memory via the AMBA 3.0 / 4.0 AXI Protocol Interconnect to an 4K/8K TFT LCD / OLED display panel.

- The video image in frame buffer memory can be 8/10/12-bit 4:2:0 or 4:2:2 or 4:4:4 sampled YCrCb video or 4:4:4 RGB. For 4:2:0 and 4:2:2 YCrCb, the chroma components are re-sampled to 4:4:4 and color converted to RGB.

-

Motorola MC6845 Functional Equivalent CRT Controller

- The DB6845 CRT Controller core is a full function equivalent to the Motorola MC6845 device.

- The DB6845 interfaces a microprocessor to a raster-scan CRT display. The microprocessor access 19 registers (1 Address and 18 Data Registers) within the DB6845 in order to provide video timing, refresh memory addresses, cursor, and light pen strobe signals.

- CRT video timing signals include Vertical Sync (VS), Horizontal Sync (HS), and Display Enable (DE) output signals. Refresh memory addressing includes Memory Address (MA[13:0]) and Row Address (RA[4:0]) output buses.

-

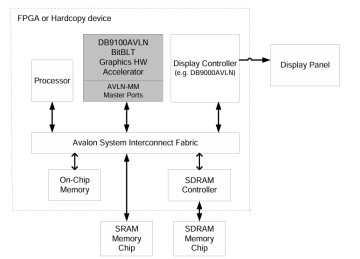

BitBLT Graphics Hardware Accelerator (Avalon Bus)

- The DB9100AVLN BitBLT Graphics Hardware Accelerator Verilog IP Core renders a graphics frame by generating new bitmaps from commands to combining existing bitmaps on and off-screen using one of 256 Raster Operations.

- A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT).

-

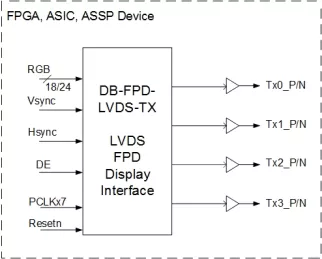

FPD LVDS Display Interface, 1 Port / 2 Port LCD Panel

- The DB-FPD-LVDS-TX LVDS Display Interface IP Core interfaces parallel 18-bit/24-bit RGB Pixel Data with display timing VSYNC, HSYNC, Data Enable, and Pixel Clock to a FPD LVDS compliant display panel via 3 or 4 or 5 LVDS Differential Data Pairs and 1 LVDS Differential Clock Pair.

-

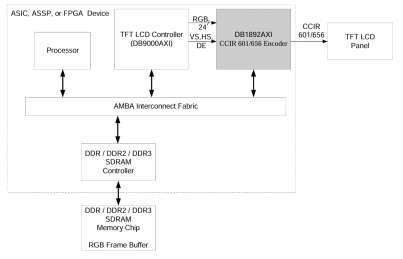

RGB to ITU-R 601/656 Encoder

- The DB1892AXI RGB to CCIR 601 / CCIR 656 Encoder interfaces RGB data along with synchronization signals from a LCD Controller (or any LCD display timing & control unit) to a TFT LCD Panel by-way-of a CCIR 601 / CCIR 656 interface.

-

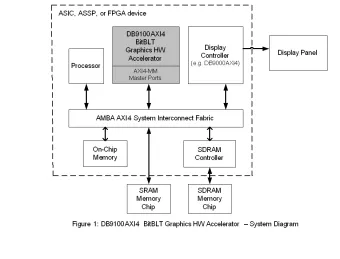

BitBLT Graphics Hardware Accelerator (AXI4 Bus)

- Bit Block Transfer – 3 Independent Memory Sources of data:

- 2D Raster Operations (ROP) performed on Block Transfers:

- BitBLT Draw Features:

- 2D Graphics Rendering Engine (Option):