DisplayPort IP

Welcome to the ultimate DisplayPort IP hub! Explore our vast directory of DisplayPort IP cores.

DisplayPort IP Cores are designed for transmission and reception of serial-digital video for consumer and professional displays. These IP cores help users to implement a DisplayPort video interface as defined by VESA DisplayPort specifications.

All offers in

DisplayPort IP

Filter

Compare

89

DisplayPort IP

from

24

vendors

(1

-

10)

-

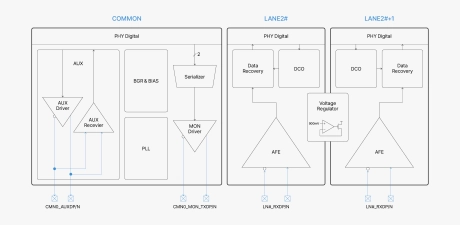

DP and eDP TX/RX PHY IP

- eDP v1.5 compliant

- Supports for 1.62Gbps to Max 8.1Gbps data rate

- PSR, PSR2 supported for low power consumption ( FW_SLEEP, FW_STANDBY supported )

- Supports for eDP v1.5 feature such as AUX-less Link Training

-

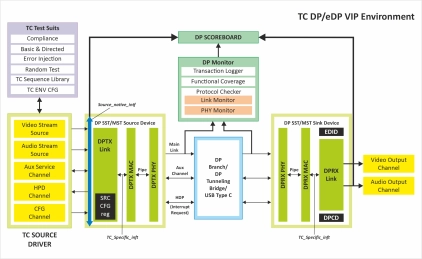

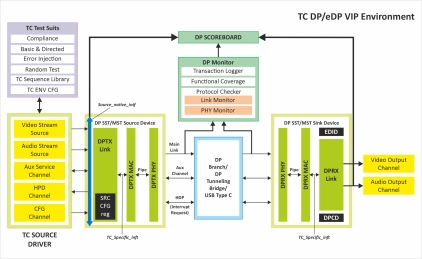

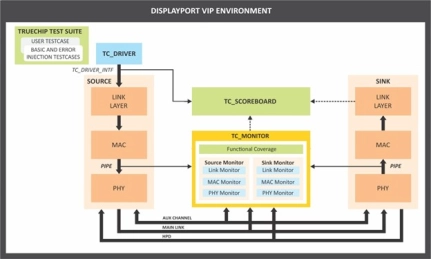

eDP 2.0 Verification IP

- The eDP 2.0 Verification IP provides an effective & efficient way to verify the components interfacing with the eDP interface of an ASIC/FPGA or SoC.

- The eDP VIP is fully compliant with the Standard eDP Version 2.0 specifications from VESA.

- This VIP is a lightweight VIP with an easy plug-and-play interface, so that there is no hit on the design time and the simulation time.

-

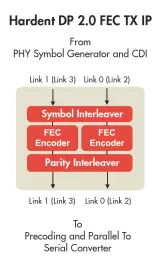

VESA DisplayPort 1.4 Forward Error Correction (FEC) Transmitter

- VESA DisplayPort 1.4 compliant

- Reed-Solomon RS (254,250) FEC, 10-bit symbols

- Two-way interleaving for 1-, 2- and 4-lane modes (4-lane mode requires 2 FEC IP core instances)

- DisplayPort main 8b/10b encoder included (Tx only)

- Status and control can be done with signals or optionally via an integrated APB register module (Rx)

-

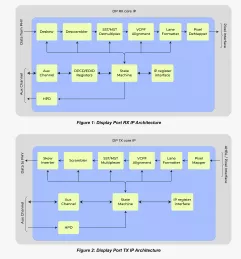

DisplayPort Transmitter & Receiver

- Compliant to Display Port 2.0/eDP1.5.

- Dynamic support for RGB / YCbCr444 / YCbCr422 / RAW and Y only formats.

- Supports multi-stream transport (MST) upto 4 streams and single stream transport (SST).

- Dynamic lane support (1, 2, or 4 lanes).

-

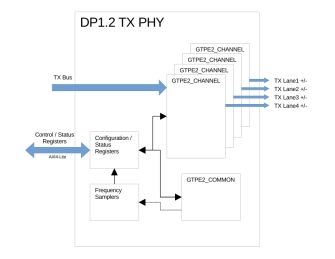

DisplayPort 1.2a TX PHY targeting 28nm Artix-7

- Supported link rates of 1.62, 2.7 and 5.4 Gbps.

- Hardware proven.

- Simulation testbench.

- Example project, including firmware which performs link initialization with the PHY

-

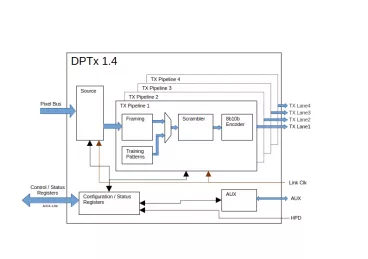

Ultra-small footprint, static framing, DPTx 1.4 IP core

- DisplayPort 1.4 compatible.

- Ultra-small footprint (1k LUT minimum, 3.5k LUT maximum).

- Hardware proven on AMD/Xilinx 28nm FPGA fabric.

-

eDP 1.5 Verification IP

- Fully compliant with VESA Embedded DisplayPort (eDP) Standard 1.5 Specification

- Supports power saving feature:- Panel Self Refresh features PSR/PSR2, PR, Adaptive sync, and backlight control.

- Supports HDCP version 1.4, 2.2 and 2.3

- Supports Alternative Scrambler Seed Reset (ASSR)

- TPS4 with ASSR is supported

-

DisplayPort 2.1 Verification IP

- Supports Isochronous transport services over the Main-Link.

- Capable Link and device management services over the AUX_CH.

- Can handle AUX transaction to access the DisplayPort Configuration Data (DPCD) address.

- Capable of handling multi stream packet and single stream packet data transmission.

-

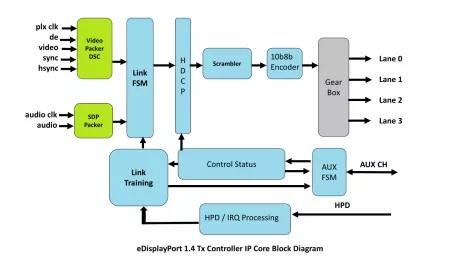

eDisplayPort v1.4 Transmitter Controller IP Core

- Supports eDP 1.4b specification

- Supports full eDP Transmitter functionality

- Supports multi lanes upto 4 lanes.

- Supports main link, Aux link and Hot plug functionality

-

DisplayPort Receiver IP

- Silicon proven on multiple ASIC and FPGA processes

- Capable of operating without a host CPU in low complexity applications

- Horizontal and vertical video delimiter signals with 1, 2 or 4 pixels per output cycle, supporting up to 16K resolution output; deep color and HDR support

- 1.62 to 8.1 Gbps link rate across 1, 2, or 4 lanes