Error Correction/Detection IP

Error Correction/Detection IP cores are specialized hardware modules designed to enhance the reliability and integrity of data transmission and storage in embedded systems. These cores implement advanced error detection and correction algorithms, such as Hamming codes, Reed-Solomon, and BCH, to identify and correct errors in data, ensuring accurate and secure communication. Ideal for applications in memory systems, communication networks, and high-performance computing, Error Correction/Detection IP cores help prevent data corruption, reduce system downtime, and improve overall system performance.

All offers in

Error Correction/Detection IP

Filter

Compare

243

Error Correction/Detection IP

from

39

vendors

(1

-

10)

-

LunaNet AFS LDPC Encoder and Decoder IP Core

- Rate 1/2

- GNSS, AFS

- Subframe 2/3/4

- Low implementation loss

-

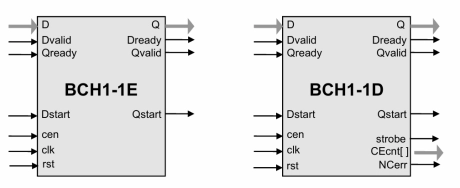

Very Low Latency BCH Codec

- High performance, low latency

- Small size (75K gates for k=298, t=4) configuration, the core uses just 17K gates in ASIC)

- Entirely self-contained (no external RAM required)

- Data inputs and outputs have flip-flops attached to the pins

-

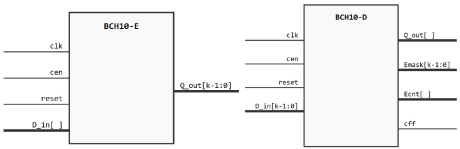

Parameterizable compact BCH codec

- Highly parameterizable

- Very low area (in the largest, n = 511 t = 16 configuration, the core uses just 17K gates in ASIC)

- Entirely self-contained (no external RAM required)

-

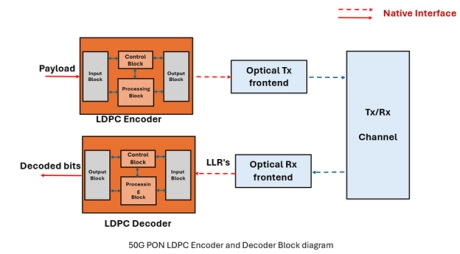

50G PON LDPC Encoder/Decoder

- Fully compliant with ITU-T G.9804 LDPC specifications

- Supports downstream and upstream FEC requirements - LDPC (17280, 14592)

- Supports Throughput up to 50 Gbps

- Supports both hard-decision and soft-decision decoding

-

SDA OCT Encoder and Decoder

- The SDA OCT Encoder handles the construction of Over-The-Air (OTA) frames as indicated in the standard, a preamble followed by a header and payload data, with both fields being protected by cyclic redundancy check (CRC) and forward error correction (FEC).

- The SDA OCT Decoder performs the synchronization of the Over-The-Air (OTA) frame and then decodes the header and payload data within the frame.

-

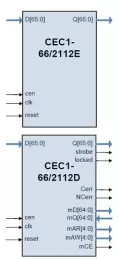

66/2112 Codec for Cyclic Code (2112,2080)

- Small Size

- Implements FEC Sublayer for 10GBASE-R (section 74 of the IEEE 802.3 standard)

- 10G/40G/100G Ethernet MAC-friendly interface

- Practically self-contained: requires only memory for one 2112-bit block in the decoder.

-

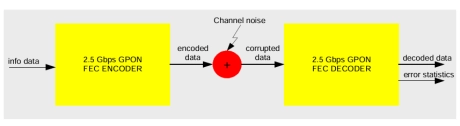

2.5 Gbps GPON FEC Codec

- This high performance core is a full featured Forward Error Correction encoder and decoder, specially designed for high speed optical networks or any other broadband applications.

- It is fully compliant with the 2.5 Gbps GPON standard (G.984.3) and is available for FPGA or ASIC implementation.

- The FEC algorithm is based on Reed-Solomon (255,239) code and consists of an encoder and decoder module.

-

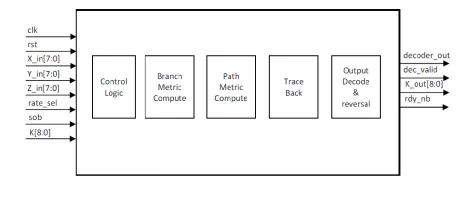

WCDMA Release 9 compliant Viterbi Decoder

- 3GPP TS 25.212 V 9.5.0 Release 9

- Supports all block sizes i.e., K=40 - 504.

- Constraint length of 9

-

-

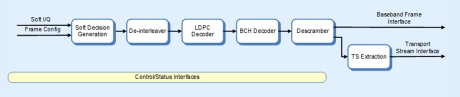

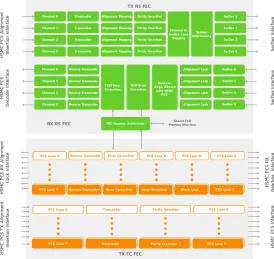

DVB-Satellite FEC Decoder

- The CMS0077 Satellite FEC Decoder has been designed specifically to meet the requirements of the DVB-S2 and DVB-S2X advanced wide-band digital satellite standards.

- The core provides all the necessary processing steps to convert a demodulated complex I/Q signal into a standard TS output stream.