RF Power Amplifier Precorrection System

DPSYS is a Digital Precorrection (Predistortion) system designed to compensate for the non-linear characteristic of a high-power …

Overview

DPSYS is a complete Digital Precorrection (Predistortion) system designed to compensate for the non-linear characteristic of a high-power RF Amplifier. The system is capable of adjusting both the gain and phase of a complex input signal. This is achieved by means of a complex multiplication of the input with a complex polynomial function stored in the LUT. Complex inputs are sampled on the rising edge of clk when en is high.

The LUT contains the inverse PA characteristic and is applied before the amplification stages (either at baseband or IF frequencies). By programming the LUT with the inverse gain/phase PA response, the resultant PA response is linearized. After linearization, the output signal is much cleaner with reduced intermodulation distortion. This is most readily observed by the absence of raised 'shoulders' at either side of the signal of interest.

The system may be used in open-loop or closed-loop configuration. For open loop operation, the LUT coefficients are static and programmed during initial setup of the PA precorrection system. For closed-loop operation, an external circuit may compare the baseband inputs and PA outputs and adjust the LUT coefficients dynamically in order to automate the linearization process.

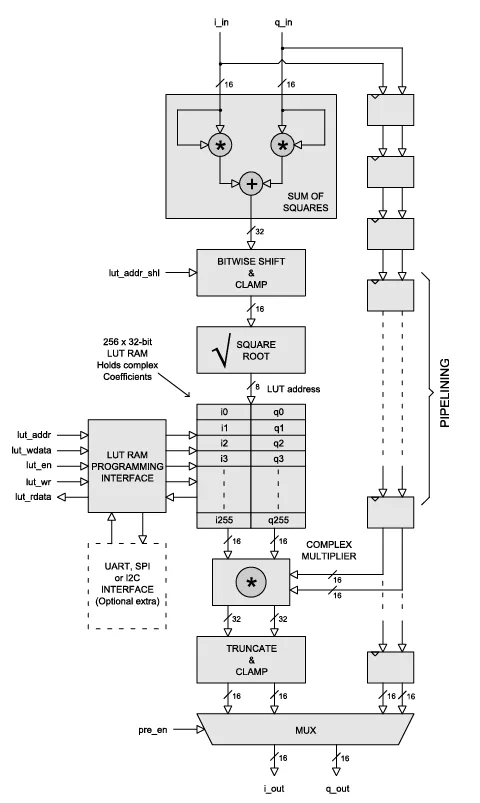

The first stage of the pipeline computes the magnitude of the complex input signal. The magnitude serves as an address into a LUT which in turn indexes a pair of complex coefficients (I & Q). The complex input is multiplied by the complex coefficients in order to modify the gain and phase of the input accordingly. Finally the output is truncated and clamped to 16-bit precision.

Key features

- Synthesizable, technology independent VHDL Core

- Compensates and corrects the non-linear characteristic of an RF Power Amplifier operating at high power levels

- Corrects both the PA Gain and Phase responses - sometimes referred to as the (AM-AM) and (AM-PM) characteristics

- Features a 256 x 32-bit LUT RAM to store the complex coefficients

- LUT may be initialized at compile time or modified during normal circuit operation

- Optional UART, I2C or SPI interface to allow easy programming via a microcontroller

- Suitable for open-loop or closed-loop operation

- LUT coefficients may be programmed 'on-the-fly' for adaptive precorrection systems

- Typically recovers up to 20dB in the output spectral 'shoulders' after the RF Power Amplifier stages

- Suitable for operation at baseband or IF frequencies

- Pipeline latency of only 8 clock cycles

- Sample rates in excess of 200 MHz

Block Diagram

Applications

- Power amplifier linearization for mobile Base-stations, Broadcasting etc.

- Precorrection of wide bandwidth signals such as UMTS, WCDMA and OFDM

- Precorrection of any type of digitally modulated signal where the signal envelope varies and therefore the instantaneous input power

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Amplifier IP core

Powering the Future of RF: Falcomm and GlobalFoundries at IMS 2025

Real-Time ESD Monitoring and Control in Semiconductor Manufacturing Environments With Silicon Chip of ESD Event Detection

Novel Trade-offs in 5 nm FinFET SRAM Arrays at Extremely Low Temperatures

Linearity Analysis of Source-Degenerated Differential Pairs for Wireline Applications

How to Elevate RRAM and MRAM Design Experience to the Next Level

Frequently asked questions about Amplifier IP cores

What is RF Power Amplifier Precorrection System?

RF Power Amplifier Precorrection System is a Amplifier IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this Amplifier?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Amplifier IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.