DMA Controller IP

Welcome to the ultimate DMA Controller IP hub! Explore our vast directory of DMA Controller IP

The Direct Memory Access (DMA) controllers enable the movement of blocks of data from peripheral to memory, memory to peripheral, or memory to memory without burdening the processor.

All offers in

DMA Controller IP

Filter

Compare

37

DMA Controller IP

from

18

vendors

(1

-

10)

-

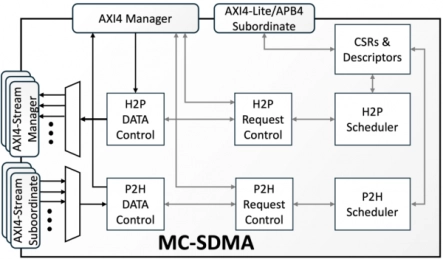

Multi-Channel Streaming DMA Controller

- The MC-SDMA IP core implements a highly configurable, bandwidth-efficient, and easy-to-use Direct Memory Access (DMA) controller that transfers data between the host system’s memory and multiple peripherals equipped with streaming interfaces.

- The core interfaces with the host memory via a manager AMBA® AXI4 (memory-mapped) port and provides access to its configuration and status registers (CSRs) via a subordinate AXI4-Lite or APB4 interface.

-

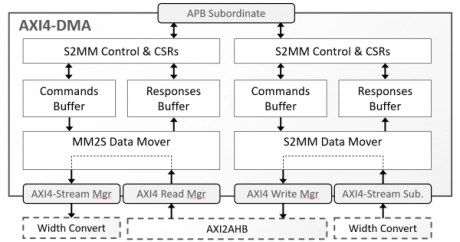

AXI4 to/from AXI4-Stream DMA

- The AXI4-DMA IP core implements a Direct Memory Access (DMA) engine that efficiently moves data between AXI4-Stream peripherals and a memory-mapped AXI4 bus.

- The core implements two independent paths: One transfers data from the read manager memory-mapped interface to the manager stream (MM2S) interface.

-

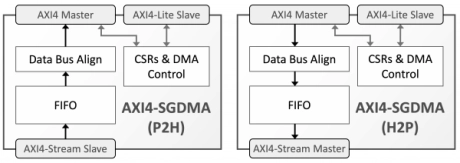

AXI4 to/from AXI4-Stream Scatter-Gather DMA

- The AXI4-SGDMA IP core implements a Host-to-Peripheral (H2P), or a Peripheral-to-Host (P2H) Direct Memory Access (DMA) engine, which interfaces the host system with an AXI4 Memory-Mapped master port and the peripheral with either a slave or a master AXI4-Stream port.

- The core operates in either Scatter-Gather (SG) Mode, reading descriptors from a run-time defined memory mapped-location, or in Direct Mode, transferring data according to a descriptor stored in local registers.

-

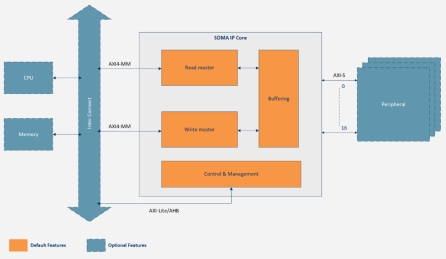

Stream Direct Memory Access (SDMA)

- The multi-channel Stream Direct Memory Access (SDMA) controller IP core provides high bandwidth direct memory access between memory and any IP peripherals with an AXI4-Stream interface for up to 16 channels.

- The SDMA IP utilities a dedicated Write and Read circular buffer structure for data and descriptor(s) for each DMA channel, which helps in offloading data movement tasks from the Central Processing Unit (CPU) in processor-based systems.

-

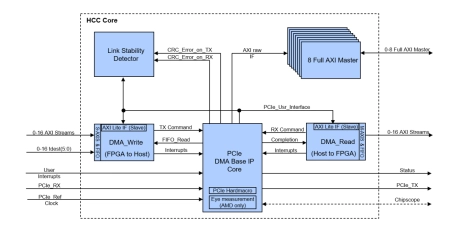

High Channel Count DMA IP Core for PCI-Express

- The High Channel Count (HCC) DMA IP core for PCI-Express is a powerful PCIe Endpoint with multiple industry standard AXI Interfaces.

- This IP addresses continuous streaming applications from up to 64 different data sources. Each channel is able to transmit data into a separate memory area.

- Up to 16 AXI Stream masters read DMA Data from the host and present it to the user logic. Additional 8 AXI4 masters are available to interface full AXI or AXI-Lite peripherals with the host.

-

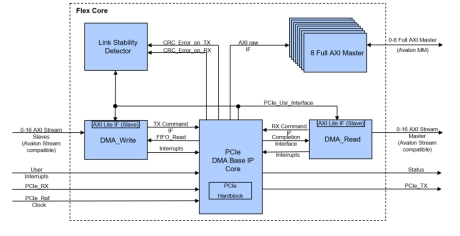

Multi-Channel Flex DMA IP Core for PCI Express

- The Multi-Channel DMA IP Core for PCI-Express is a powerful PCIe Endpoint with multiple industry standard AXI Interfaces.

- Up to 16 independent AXI Stream Slaves write DMA Data to the Host. Up to 16 AXI Stream Masters read DMA Data from the Host and present it to the User Logic.

- Each channel operates on a separate memory area. Additional 8 AXI4 Masters are available to interface full AXI or AXI-Lite peripherals with the Host.

-

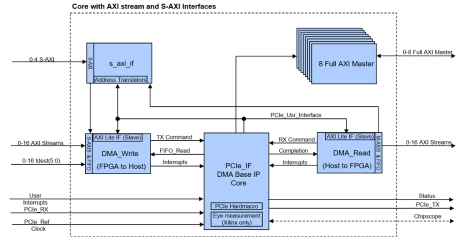

AXI Bridge with DMA for PCIe IP Core

- The AXI Bridge with DMA IP core is the ultimate PCIe DMA IP solution with a powerful mix of multiple industry standard AXI Interfaces.

- AXI Stream interfaces allow continuous data streaming from FPGA to Host or from Host to FPGA. S-AXI Memory mapped interfaces allow easy data access of remote memories in order to realize shared memory access or per to peer applications.

-

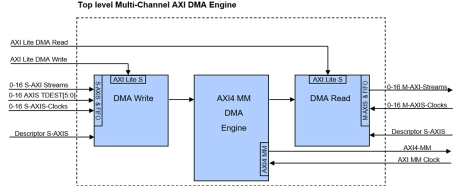

Multi-Channel AXI DMA Engine

- The Multi-Channel AXI DMA engine IP Core for AXI4 is a powerful programmable AXI Stream to AXI memory mapped bridge with sophisticated data addressing options.

- These features allow data accesses on a tile basis in order to address regions of interest (ROI) based applications like stereo cameras, 2D picture compression algorithms and others.

-

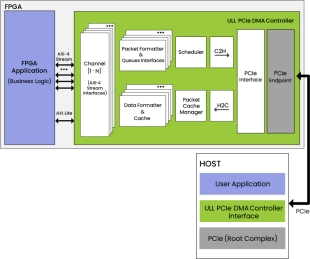

ULL PCIe DMA Controller

- The ULL PCIe DMA Controller is a high-performance, bidirectional data transfer solution. It is designed for seamless communication between FPGAs and host CPUs over PCIe.

- With a round-trip time as low as 585ns*, this IP core empowers developers to maximize resource utilization and achieve ultra-low latency without compromising performance.

-

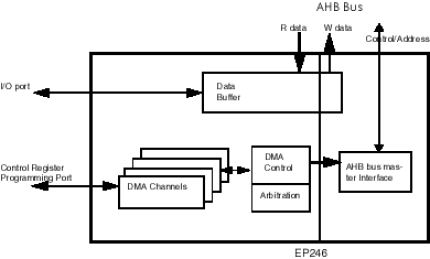

AMBA AHB Direct Memory Acess (DMA) Controller

- Multiple independent DMA channels with direct AHB bus interface.

- DMA transfers between AHB memory devices and I/O ports.

- Scatter-gather allows DMA to merge multiple data source to contiguous space.

- Supports both hardware initiated transfer and software initiated transfer.