HDLC IP

Welcome to the ultimate HDLC IP hub! Explore our vast directory of HDLC IP

All offers in

HDLC IP

Filter

Compare

9

HDLC IP

from

7

vendors

(1

-

9)

-

High-Level Data Link Controller

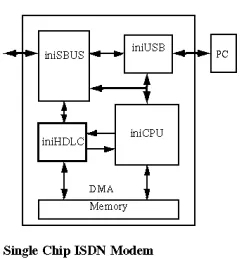

- Inicore's iniHDLC family of High-Level Data Link Controller (HDLC) cores consist of a Receiver (FPR: From Primary Rate) and a Transmitter (TPR: To Primary Rate) unit.

- These single channel HDLC controllers handle all interframe flags, delimiting flags and Frame Check Sequence (FCS) pattern.

-

HDLC & SDLC Protocol Controller

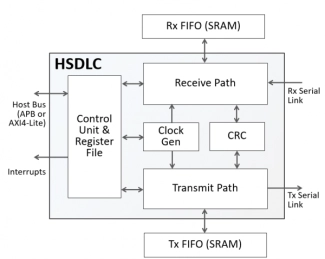

- The HSDLC IP core implements a controller for the High-Level Data Link Control (HDLC) and the Synchronous Data Link Control (SDLC) protocols.

- It is based on the Intel® 8XC152 Global Serial Channel (GSC) working in SDLC mode, and adds features to support HDLC or proprietary frame transmission under host processor control.

- The core operates as a peripheral to a host processor, and is easy to integrate with both modern and legacy processors.

-

Used for controlling HDLC/SDLC transmission protocols

- Two separate receiver and transmitter interfaces.

- Two separate, configurable FIFO buffers for receiver and transmitter

- Bit stuffing and unstuffing

- Address recognition for receiver and address insertion for transmitter

-

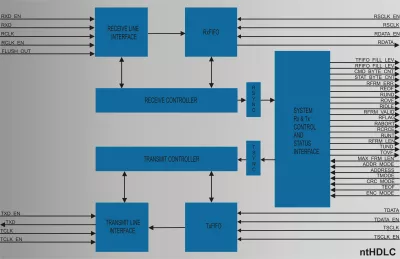

Single Channel HDLC Controller

- Single port synchronous serial line interface.

- Flag/Abort Generation/Detection.

- Zero Insertion/Deletion.

- Non-octet alignment detection.

-

Enhanced Multiprotocol Serial Communication Controller

- Rapid prototyping and time-to-market reduction

- Design risk elimination

- Development costs reduction

-

HDLC/SDLC controller

- Two separate receiver and transmitter interfaces.

- Two separate, configurable FIFO buffers for receiver and transmitter

- Bit stuffing and unstuffing

- Address recognition for receiver and address insertion for transmitter

-

HDLC Framer

- Best-in-Class size and performance, supports many thousands of channels.

- Supports bit-synchronous and byte-synchronous HDLC.

- Generates/Accepts data for multiple independent TDM HDLC streams. Generates/Removes flag characters to delineate HDLC frames.

- Inserts/Removes HDLC bit or byte stuffing. Provides variable width data output.

-

Async/HDLC Serial Channel

- Async mode with optional address and parity bit

- HDLC mode with Flag generation, CRC and Abort capability

- Digital PLL and data encode/decode

- Four bytes of buffering for both receive and transmit