Other

All offers in

Other

Filter

Compare

47

Other

from

16

vendors

(1

-

10)

-

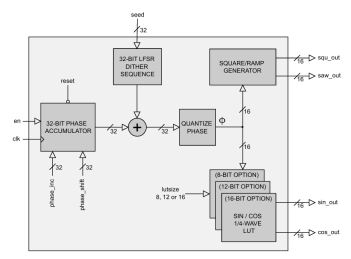

Direct Digital Synthesizer / Periodic waveform generator

- The DDS IP Core is a high-precision Direct Digital Synthesizer2 used for the generation of periodic waveforms.

- On each rising-edge of the sample clock and when the clock-enable is high, the phase in the phase accumulator is incremented by the value phase_inc.

- This phase is quantized to 16-bits and passed as an address to a look-up table which converts the phase into a waveform.

-

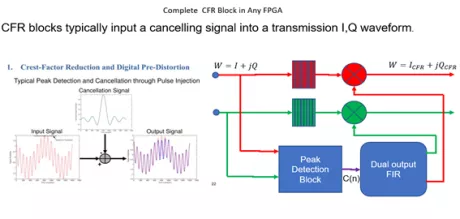

RF Power Amplifier Precorrection System

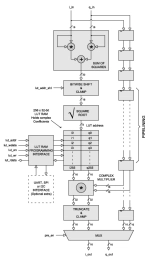

- DPSYS is a complete Digital Precorrection (Predistortion) system designed to compensate for the non-linear characteristic of a high-power RF Amplifier.

- The system is capable of adjusting both the gain and phase of a complex input signal.

- This is achieved by means of a complex multiplication of the input with a complex polynomial function stored in the LUT. Complex inputs are sampled on the rising edge of clk when en is high.

-

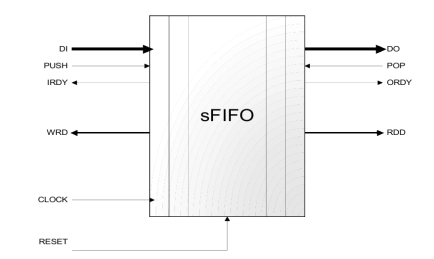

Synchronous FIFO with configurable flags and counts

- The sFIFO controls are designed to operate over a wide range of clock frequencies.

- The interface signals are fully synchronous; no asynchronous signals are present on either side. Only reset may be asynchronous in that it may be asserted asynchronously and synchronized internally to the clock.

-

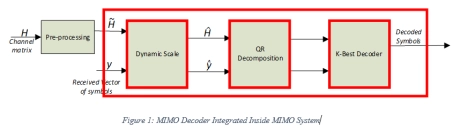

MIMO Decoder

- Includes QR Decomposition, Dynamic scale and K-best Decoder

- Fixed Depth K-Best Decoder (K=16)

- Achieves close-to ML BER performance

- Supports synchronized streams with different QAM (from BPSK to 64 QAM) dependent on MIMO mode

- Supports square and non-square QAM

-

MIMO Sphere Decoder

- Fixed Complexity Sphere Decoder providing fixed throughput

- Achieves close-to ML BER performance

- MATLAB and C model for – MIMO 2×2 and 4×4 – Can be modified to support other MIMO sizes – BPSK, 4-QAM, 16-QAM and 64-QAM

- Efficient and optimized FPGA Architecture (4×4 MIMO, 16-QAM)

-

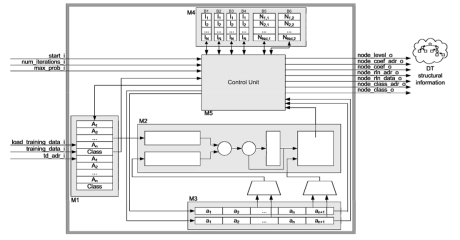

Decision tree inference core

- So_ip_idt core can be used create a decision tree directly in hardware. It can create DTs with univarite, multivariate and non-linear tests.

- Creating DTs directly in hardware results in the significant increase of DT inference speed, compared with the traditional software-based approach.

-

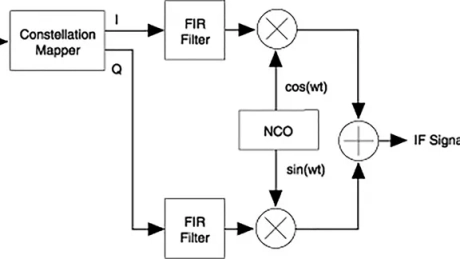

NCO Intel® FPGA IP Core

- A numerically controlled oscillator (NCO) is a digital signal generator, which synthesizes a discrete-time, discrete-valued representation of a sinusoidal waveform

- You can typically use NCOs in communication systems

- In such systems, they are used as quadrature carrier generators in I-Q mixers, in which baseband data is modulated onto the orthogonal carriers in one of a variety of ways.

-

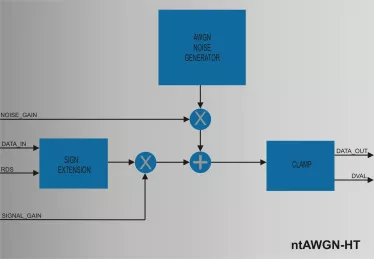

High Throughput Additive White Gaussian Noise Generator

- High precision AWGN Channel emulator.

- Programmable Pseudo Random Generator(LFSR).

- Programmable number of output bits.

- Support of throughput rates up to 10 Gbps.

-

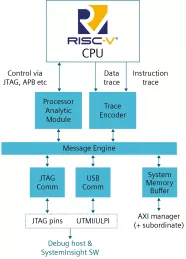

Tessent RISC-V trace and debug

- Instruction trace

- Efficient packet format

- Fast profiling

- Multiple retirement

-