Other

All offers in

Other

Filter

Compare

308

Other

from

37

vendors

(1

-

10)

-

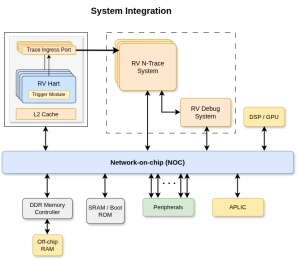

RISC-V Debug & Trace IP

- 10xEngineers Debug & N-Trace IP delivers a unified Debug + Trace solution that provides full-system visibility with low overhead and multi-hart awareness.

- Standards-compliant debug, real-time trace, and flexible triggering significantly reduce bring-up time and simplify system integration.

-

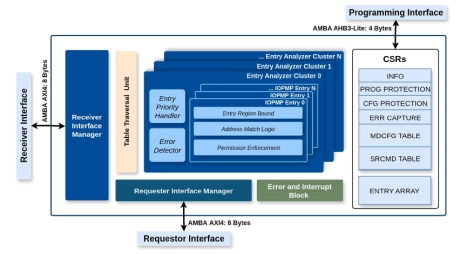

RISC-V IOPMP IP

- The I/O Physical Memory Protection (IOPMP) unit is a hardware-based access control mechanism designed to safeguard memory regions in RISC-V SoCs.

- It ensures only authorized devices and masters can access sensitive memory areas, enabling secure and reliable system operation.

-

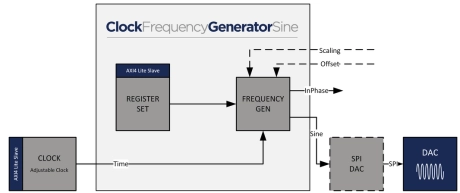

Sine Wave Frequency Generator

- The Sine Wave Frequency Generator is a time and frequency aligned sine wave frequency generator allowing any frequency to be generated between 1Hz and 200kHz adjustable in 1Hz steps.

- It uses the vendor's Adjustable Clock core as source for source synchronous frequency generation. It provides either a parallel DAC interface or a serial highly configurable SPI interface to access a DAC.

-

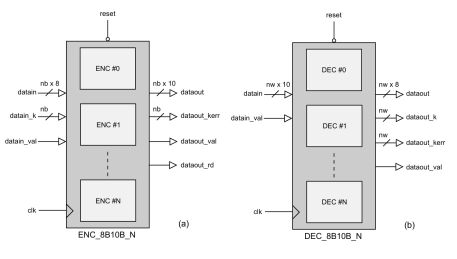

8b/10b Encoder/Decoder

- The CODEC_8B10B IP Core is a scalable 8B/10B Encoder/Decoder pair suitable for a wide range of serial data transmission applications.

- The design is optimized for very high-speed operation and is suitable for use in serial data links of 6 GHz+ on basic FPGA devices.

-

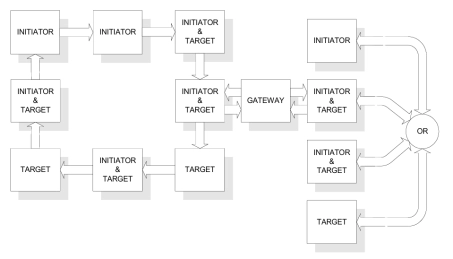

Register, Configuration and Control Bus

- A2R provides an interconnection mechanism between control registers in an ASIC design and any number of control devices; CPUs, debug ports etc..

- The bus is especially suited for synthesizable designs. It is specifically developed to meet the challenges of long interconnect delays in large System-on-chip designs and can be tailored to match system clock rates.

-

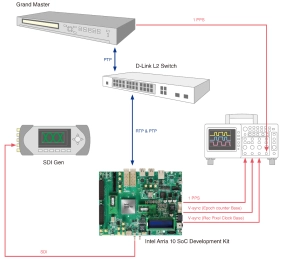

ST2059-1&2 IP

- This IP generates a timing signal standardized in SMPTE ST 2059 using IEEE1588v2 Precision Time Protocol (PTP).

- The timing signal is utilized as “GenLock” signal which has been used in conventional A/V system.

-

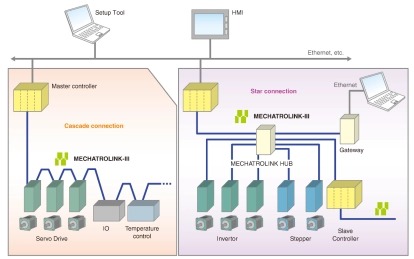

MECHATROLINK-III Master/Slave IP

- Functionally compatible with JL-100 which is the ASIC for MECHATROLINK-III Master/Slave communication.

- Parameters required for MECHATROLINK-III communication are set either by cpu or through external pins.

-

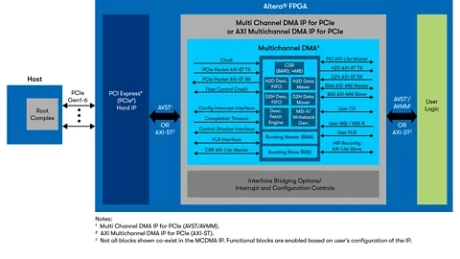

Multichannel DMA Intel FPGA IP for PCI Express*

- The Multichannel DMA IP for PCI Express provides high efficiency, speed, and configuration flexibility to support various applications from HPC, cloud, networking, to embedded

- With support for up to 2048 channels and Linux-based PCIe drivers provided, this low latency, low resource utilization solution is essential in handling movements of large volumes of data to optimize system performance.

-

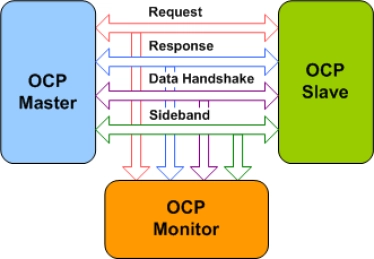

OCP Verification IP

- Compliant with OCP 3.1 specification.

- Supports OCP Master, OCP Slave, OCP Monitor and OCP Checker.

- Supports all OCP protocol transfer & command types.

- Supports all OCP protocol signal widths including address and data.

-

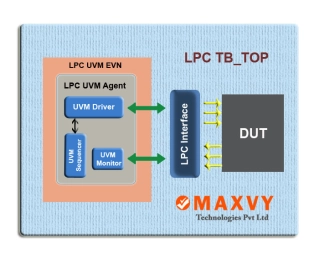

Low Pin Count (LPC) controller verification IP

- The Low Pin Count (LPC) interface is a low bandwidth bus with up to 33 MHz performance

- It is used to connect peripherals around the CPU and to replace the Industry Standard Architecture (ISA) bus which can only run up to 8 MHz

- The primary benefit is that signals can be transmitted across a minimum of seven traces for an LPC bus versus 52 traces for an ISA bus

- This relieves the pressure of routing on the often-congested motherboard and at the same time improves the overall system integrity