Clock Generator IP

Welcome to the ultimate Clock Generator IP hub! Explore our vast directory of Clock Generator IP

All offers in

Clock Generator IP

Filter

Compare

10

Clock Generator IP

from

7

vendors

(1

-

10)

-

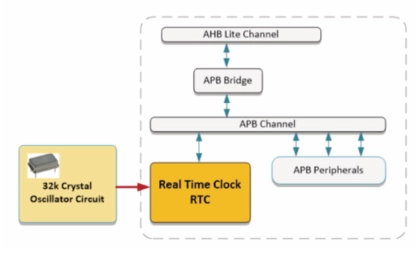

APB Real Time Clock

- The Real Time Clock (RTC) is a clock-calendar IP core that keeps track of the “Time of Day”.

- The core is organized as a series of BCD counters that counts Seconds, Minutes, Hours, Days, Months and Years (Time Units).

- The RTC seconds counter time base is generated from a clock input that is separate from the system clock.

-

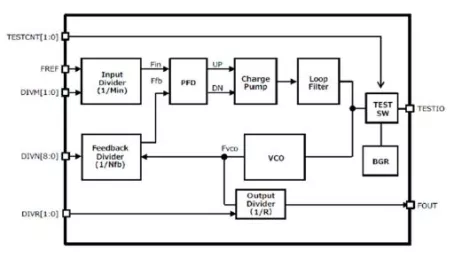

High Speed Integer PLL IP

- Up to 4Ghz clock output

- Wide range of multiplicand

- Small physical area

- TEST pin integrated

-

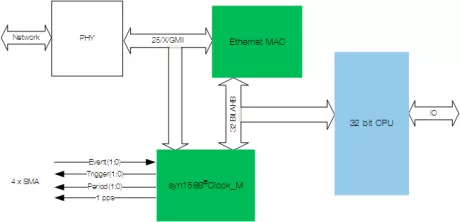

syn1588® enabled IEEE 1588 compliant clock synchronisation

- fully synchronous to the system clock

- all registers of the core operate with the rising clock edge

- well commented, structured VHDL source code

- medium footprint and medium I/O count

-

Real Time Clock

- The RTC (Real Time Clock) provides an automatic wake-up to manage all low-power modes.

- It is an independent timer. The RTC provides a set of continuously running counters which can be used, with suitable software, to provide a clockcalendar function.

-

Low noise from 8GHz to 11.3GHz differential LC VCO

- Phase noise -108dB typical

- Single 1.2V Power Supply

- VCO center frequencies 8.5GHz, 10.0GHz, 10.7GHz, 11.1GHz

- Each VCO frequency tuning ±8%

-

30GHz VCO in SiGe

- Center frequency (GHz): 20, 24, 25, 26, 30

- Tuning range: 10%

- Tuning voltage input: 0 … +3.3V

- Phase noise: -105dBc @ 1MHz offset

-

25GHz VCO in SiGe

- Center frequency (GHz): 20, 24, 25, 26, 30

- Tuning range: 10%

- Tuning voltage input: 0 … +3.3V

- Phase noise: -105dBc @ 1MHz offset

-

20GHz VCO in SiGe

- Center frequency (GHz): 20, 24, 25, 26, 30

- Tuning range: 10%

- Tuning voltage input: 0 … +3.3V

- Phase noise: -105dBc @ 1MHz offset

-

Run Time Phase Alignment Circuit

- 1. Sync Clock Generation in one clock duation.

- 2. Generatted clock is Phase Aligned with the incoming data. Data can be received.

- 3. Tx and Rx Clock can be up to +/-5% off of the frequency range. This block can accomode and can generate same tx freq at the rx side.

- 4. This Rx Clock can be used to -

-

High-Speed Digital PLL (0.5-7.5 GHz) in TSMC 40G CMOS

- Wide range and programmability (0.5GHz to 7.5GHz)

- Predictability

- Easy Porting

- Size (0.11mm^2)