USB IP

Welcome to the ultimate USB IP hub! Explore our vast directory of USB IP

All offers in

USB IP

Filter

Compare

695

USB IP

from

46

vendors

(1

-

10)

-

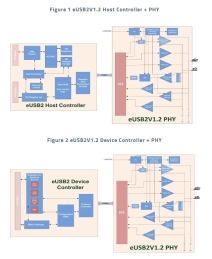

eUSB2V1.2 Controller + PHY IP

- eUSB2 can support USB high-speed, full-speed, and low-speed operation, as well as the USB 2.0 L1/L2 link power management requirements. In addition, eUSB2 requires no change to the existing USB 2.0 software programming model.

- eUSB2 also uses the same two data line configurations, eD+ and eD- as USB2 D+ and D-. Vbus and power delivery are not impacted by eUSB2.

-

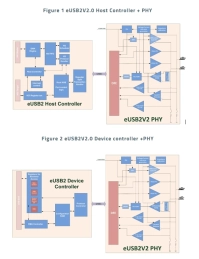

eUSB2V2.0 Controller + PHY IP

- While traditional eUSB2 meets basic connectivity needs at 480 Mbps, modern SoCs and peripherals demand significantly higher throughput.

- eUSB2-V2.0 bridges this gap by delivering up to 10× performance improvement, along with better power efficiency and EMI control — without changing the fundamental USB 2.0 software ecosystem.

-

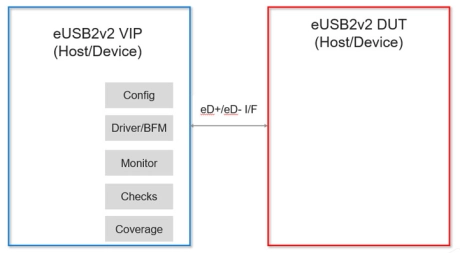

Simulation VIP for eUSB2V2

- The Verification IP (VIP) for eUSB2v2 is a complete VIP solution for the embedded USB2 (eUSB2) version 2.0.

- It provides a mature and comprehensive verification IP (VIP) for the eUSB2v2 protocol.

- Incorporating the latest protocol updates, the eUSB2v2 VIP is not only a complete bus functional model (BFM) for the eUSB2v2 DUT, but it also provides integrated automatic protocol checks and coverage models.

-

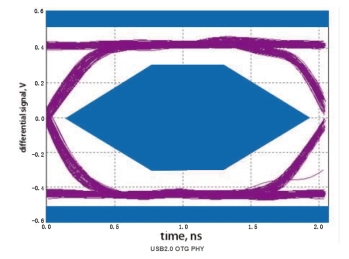

USB PHY Solution

- Brite provides USB2.0 OTG PHY which is a complete mixed-signal IP solution designed to implement OTG connectivity for a System-on-Chip (SoC) design.

- The USB2.0 OTG PHY supports the USB2.0 480Mbps protocol and data rate, and is backward compatible with the USB 1.1 1.5Mbps and 12Mbps protocol and data rates.

- It has been verified by a number of end products, especially suitable for the current popular internet of things applications.

-

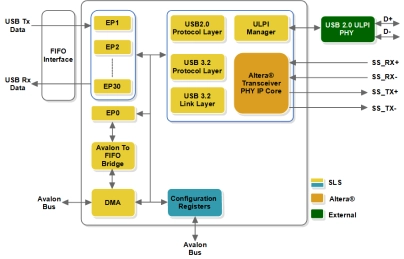

USB 20Gbps Device Controller

- Leveraging the benefits of USB 10Gbps and 5Gbps device controller, USB 20Gbps is designed using the FPGA built-in transceiver.

- It is a one-stop solution for all USB requirements ranging from USB 3.2 to USB 2.0.

- It supports SuperSpeed+ (SSP x2/x1), SuperSpeed (SS), High Speed (HS) and Full Speed (FS) communication modes.

-

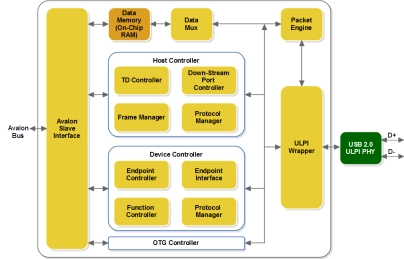

USB 2.0 On-The-Go (USB20OTG)

- The USB 2.0 On-The-Go (OTG) IP Core is a 32-bit Avalon interface compliant core and supports ULPI interface.

- It supports both USB Host and USB Device peripheral functionality.

- While acting as USB Host, it supports High Speed (HS), Full Speed (FS) and Low Speed (LS) modes.

- While acting as USB Device peripheral, it supports High Speed (HS) and Full Speed (FS) modes.

-

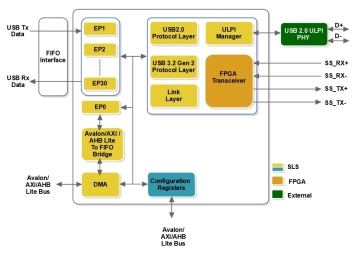

USB 10Gbps Device Controller

- Leveraging the benefits of USB 3.2 Gen 1 device controller, USB 3.2 Gen 2 is designed using the FPGA built-in transceiver.

- It is a one-stop solution for all USB requirements ranging from USB 3.2 to USB 2.0.

- It supports SuperSpeed+ (SSP), SuperSpeed (SS), High Speed (HS) and Full Speed (FS) communication modes.

-

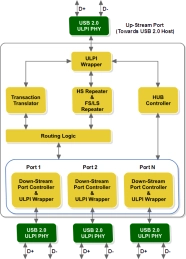

USB 2.0 HUB (USB20HUB)

- The USB 2.0 Hub IP core provides a link between the USB2.0 Host and multiple USB peripherals via UTMI + Low pin interface (ULPI).

- It supports High speed, Full speed and Low speed peripheral devices.

- Its rich features and ease of use makes it more suitable for embedded applications.

-

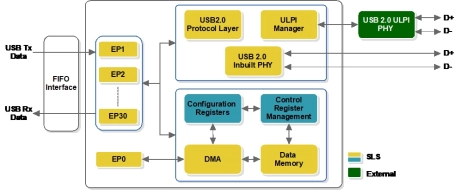

USB 2.0 Device with FIFO Interface (USB20HF)

- USB 2.0 device, FIFO interface (USB20HF) IP Core provides FIFO interface for endpoints and ULPI interface for Host communication.

- It supports 15 IN and OUT endpoints as per the USB standards which are configurable in Bulk, Interrupt and Isochronous modes as per the requirement.

- The core supports High Speed (480 Mbps), Full Speed (12 Mbps) and Low Speed (1.5 Mbps) functionality. It comes with three pre-configured endpoints - Control, Bulk IN, and Bulk OUT.

-

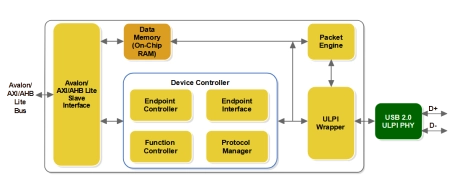

USB 2.0 Device, Software based enumeration RAM Interface (USB20SR)

- The USB 2.0 Device, Software Enumeration (USB20SR) IP Core is a RAM based USB 2.0 device core with 32-bit Avalon/AXI/AHB Lite interface and ULPI interface support.

- The core supports High Speed(480 Mbps) , Full Speed(12 Mbps) and Low Speed(1.5 Mbps) functionality.