SD/eMMC IP

Welcome to the ultimate SD IP hub! Explore our vast directory of SD IP

All offers in

SD/eMMC IP

Filter

Compare

101

SD/eMMC IP

from

21

vendors

(1

-

10)

-

Samsung 8LPU 3.3V SD/eMMC PHY

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

GF 22FDX 1.8V/3.3V SD/eMMC PHY AG2 Platform

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

Intel 16 SD/eMMC PHY North/South Poly Orientation

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC 22ULL 1.8V/3.3V SD/eMMC PHY AG2

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC N3E SD/eMMC PHY North/South Poly Orientation

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

TSMC N3P SD/eMMC PHY North/South Poly Orientation

- Synopsys SD/eMMC PHY provides an optimal balance for cost and performance for storage solutions

- Synopsys SD/eMMC PHY is a hard IP that can be used to implement a single interface that can accomplish 4-bit, 8-bit eMMC & 4-bit SD operations

- It includes an optional digi logic circuitry which is required for high-speed operations

- It complies with eMMC 5.1 (JESD84-B51A) and SDIO 6.0 JEDEC standards

-

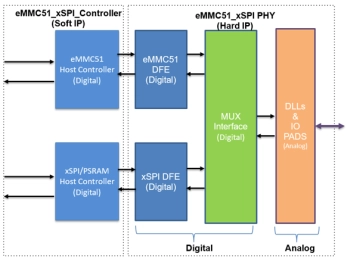

xSPI + eMMC Combo PHY IP

- This IP integrates both xSPI (Expanded Serial Peripheral Interface) and eMMC 5.1 PHY (Physical Layer) into a single unified solution, enabling support for two distinct memory protocols within the same IP.

- By combining the PHY layers for both interfaces, the design simplifies system integration, reduces area and pin count, and enhances design flexibility for SoCs that require both boot and high-speed storage functionality.

-

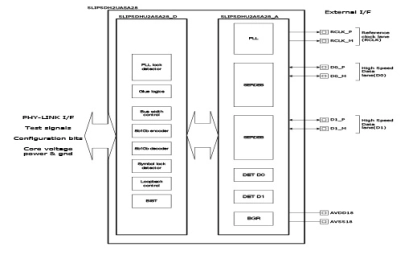

SD4.x UHSII

- Fully compliant with UHSII specification Ver. 4.x

- Bidirectional receiver/transmitter (2 channels) supporting both full and half duplex modes

- Supports data rates from 390Mbps to 1.56Gbps/ch

- RCLK frequency: 26 to 56MHz

- Built-in PLL and clock recovery

-

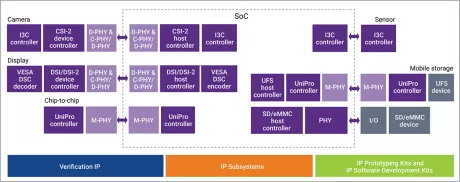

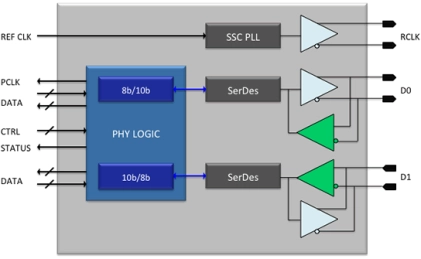

UHS-II PHY Core IP

- The UHS-II PHY IP is a comprehensive, silicon-proven configurable core that has been ported to multiple process nodes and leading foundries.

- It uses sub-LVDS signaling consisting of one pair each for transmit, receive, and an additional reference clock. This low-pin interface has reduced power consumption and low EMI.

- To further reduce power, the reference clock operates at 1/15 or 1/30 of the data transfer speed.

-

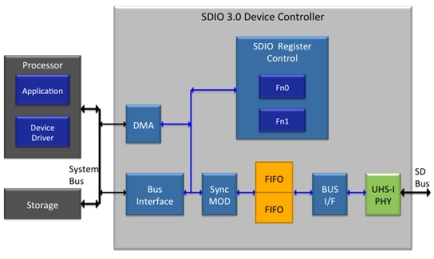

SDIO Card Device IP

- The SDIO Card Device IP core is used to implement SDIO cards that are connected to a Host processor over a standard SD bus. The flexible architecture of the SDIO Device IP core is targeted to develop a range of portable, low-power cards such as the WiFi (802.11), GPS, WiMAX, UWB, LTE.

- The SDIO Card Device IP core is fully compliant with the SD Specification Part E1 SDIO 3.0. It supports SPI, SD1, and SD4 bit transfer modes, and multiple functions per card. High-speed and full-speed SD data transfers are also supported.