DSP Core IP

Welcome to the ultimate DSP Core IP hub! Explore our vast directory of DSP Core IP

All offers in

DSP Core IP

Filter

Compare

26

DSP Core IP

from

11

vendors

(1

-

10)

-

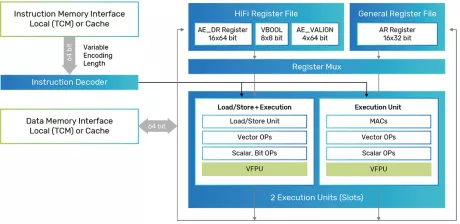

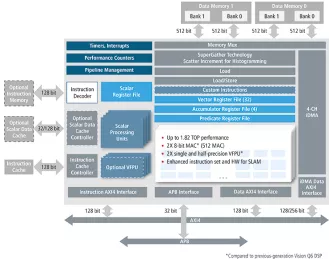

HiFi iQ DSP

- 8X Increased AI Performance: Run the entire voice AI networks efficiently with configurable AI-MAC

- 2X Increased Raw Compute Performance: Wider SIMD allows more computations

- Expanded Data Type Support: Efficiently run cutting-edge voice AI models in FP8, BF16, and more

-

Ultra-low-power Processor based on RISC-V Architecture

- The icyflex-V processor is a new ultra-low-power core based on the RISC-V 32-bit ISA, compatible with off-the-shelf open-source and/or proprietary programming tools.

- This new development represents a cost effective yet performing alternative to proprietary cores for next-generation ultra-low-power system-on-chip developments.

- The core was optimized for performance, code density and power consumption and delivers up to 3.2 CoreMark/MHz while consuming as low as 14 uA/MHz in TSMC 55 nm low-power process.

-

-

Tensilica HiFi 1 DSP

- Cycle and energy efficient for Bluetooth and Bluetooth Low Energy (BLE) codecs for speech and music

- Efficient neural network acceleration ISA and architecture support

-

Tensilica Vision Q7 DSP

- Doubles Vision and AI Performance for Automotive, AR/VR, Mobile and Surveillance Markets

-

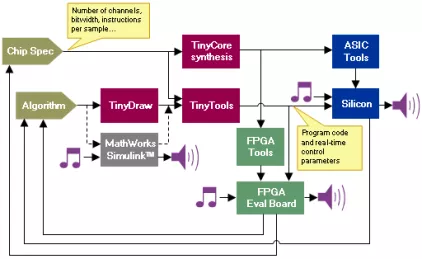

Low-power, low-gate-count, highly-configurable DSP core for audio and control processing

- A comprehensive design environment and toolset

- Very fast work-flow through the use of high-level front-end hierarchical Graphical Programming Environment, Core Synthesis and back-end “Tuning” tools

-

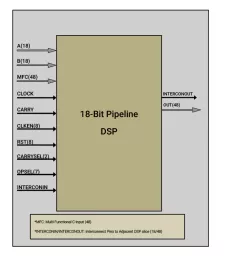

18-Bit Pipeline DSP Slice IP

- Timing resolution: 80ps

- Operating frequency range: 160MHz – 700 MHz

- Lock time: 11 cycles

- Generates user configurable precise phase shifts from 00 to 3600 with a resolution of 10

-

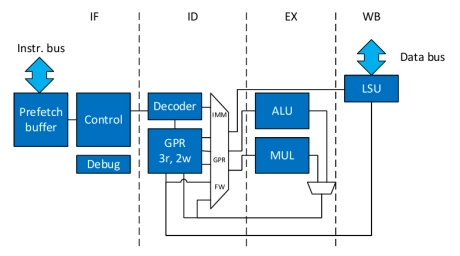

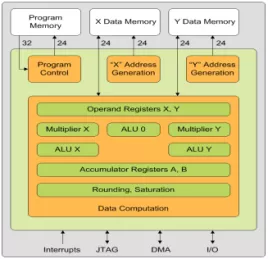

Ultra low power C-programmable Baseband Signal Processor core

- Ultra low power consumption

- Highly optimizing C-compiler software toolkit

- Minimal core size (65k gates), excluding debug interface (6k gates)

- Small memory footprint

-

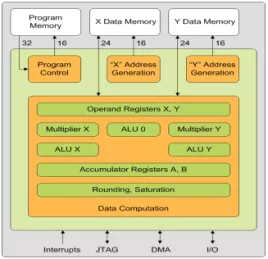

Ultra low power C-programmable DSP core

- Ultra low power consumption

- Highly optimizing C-compiler software toolkit

- Minimal core size (43k gates), excluding debug interface (6k gates)

- Small memory footprint

-

Tensilica Vision P1 DSP

- 256/128b Load/Store capabilities

- 128 8-bit MAC

- 8/16/32-bit fixed-point processing

- Single-precision (FP32) and half-precision (FP16) floating-point processing