Fast Fourier Transform IP Core

The Fast Fourier Transform IP Core implements the Decimation in Frequency - Fast Fourier Transform based on the Cooley-Tukey algo…

Overview

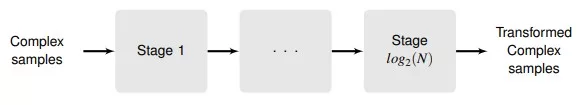

The Fast Fourier Transform IP Core implements the Decimation in Frequency - Fast Fourier Transform based on the Cooley-Tukey algorithm. The FFT/IFFT core expects complex samples as input and provides transformed complex samples as output. It performs the transform using log₂ (transform length) stages in pipeline.

Key features

- Supports forward and inverse complex FFT

- Supports transform length (N) from 23 to 2¹⁶

- Supports scaled or unscaled IFFT output

- Implemented as pipelined streaming IO architecture

Block Diagram

Benefits

- Run-time configuration of the transform mode (Forward or Inverse FFT) and transform length

- Continuously stream input and output data. The core starts processing immediately after receiving the first sample and does not wait until it receives the entire frame

- Twiddle factors can be stored in ECC ROMs

- Low-power and low-complexity design

- AXI4-Stream handshaking interfaces for seamless integration

- Works with the Creonic DVB-S2X Multi-Carrier Demodulator and Creonic DVB-RCS2 Multi-Carrier Receiver

- Available for ASIC and FPGAs (AMD Xilinx, Intel and Microchip on request)

Applications

- Multi-Carrier Transmitter and Receiver Systems

- Spectrum Analysis

- Signal Filtering

- Data Compression

What’s Included?

- VHDL source code or synthesized netlist

- HDL simulation models e.g. for Aldec’s Riviera-PRO

- VHDL testbench

- Bit-accurate Matlab, C or C++ simulation model

- Comprehensive documentation

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Filters Transforms IP core

No size fits all for signal processing on FPGA (RF Engines)

Employing general-purpose processors for radio DSP

Do's and Don'ts of Architecting the Right FPGA Solution for DSP Design

10 FPGA Design Techniques You Should Know

How to implement double-precision floating-point on FPGAs

Frequently asked questions about Filters and Transforms IP cores

What is Fast Fourier Transform IP Core?

Fast Fourier Transform IP Core is a Filters Transforms IP core from Creonic listed on Semi IP Hub.

How should engineers evaluate this Filters Transforms?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Filters Transforms IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.