SPI IP

Welcome to the ultimate SPI IP hub! Explore our vast directory of SPI IP

All offers in

SPI IP

Filter

Compare

83

SPI IP

from

23

vendors

(1

-

10)

-

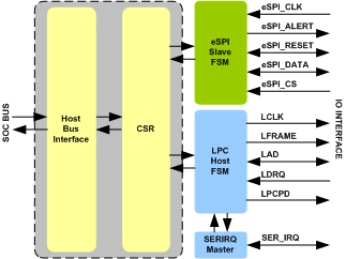

eSPI LPC Bridge IIP

- Compliant with version 1.1 LPC Interface Specifications and eSPI base specification as defined in Enhanced Serial Peripheral Interface (eSPI) Specification rev.1.0

- Converts eSPI Peripheral Channel Transactions into LPC Memory write or read instructions

- Supports full LPC host capability

- Supports SOC Slave

-

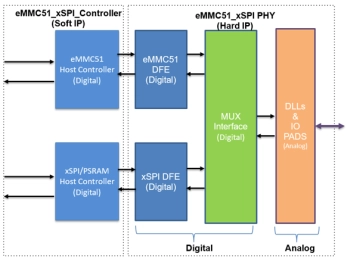

xSPI + eMMC Combo PHY IP

- This IP integrates both xSPI (Expanded Serial Peripheral Interface) and eMMC 5.1 PHY (Physical Layer) into a single unified solution, enabling support for two distinct memory protocols within the same IP.

- By combining the PHY layers for both interfaces, the design simplifies system integration, reduces area and pin count, and enhances design flexibility for SoCs that require both boot and high-speed storage functionality.

-

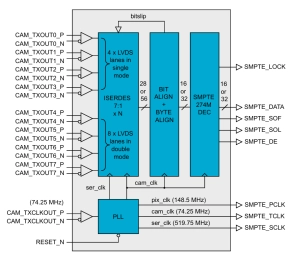

Sony Camera LVDS Interface

- The SONY_CAM_IF IP Core provides a simple way to connect the Sony® FCB-EV range of cameras to your FPGA.

- It serves as a direct replacement for an external LVDS receiver IC and takes advantage of the fast LVDS I/O solutions provided by modern FPGA devices.

-

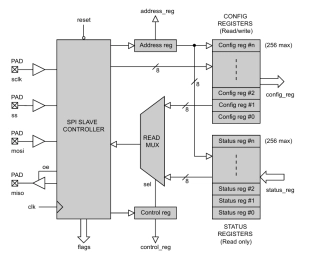

SPI Slave Serial Interface Controller

- The SPI_SLAVE IP Core is an SPI compliant slave interface controller. The controller decodes the bus signals and de-serializes them into a series of 8-bit bytes.

- Communication with the slave controller is achieved by programming a single control register and a single address register.

-

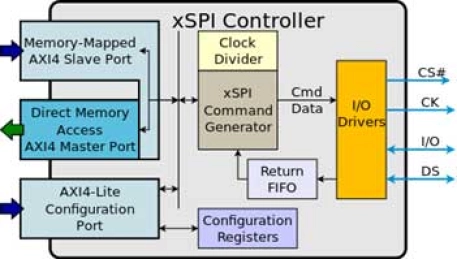

xSPI Master IP | NOR IP

This Universal NOR Flash IP supports a variety of NOR Devices and multiple Protocols, combines ease of use with high reliability, low power and speed under all conditions, including automotive applications.

The xSPI master IP supports the xSPI JESD251 standard from a standard AXI4 slave interface, and also features backwards compatibility support for Octal SPI, QSPI, DSPI, and SPI interfaces. Also supports JEDEC SFDP Standard.

-

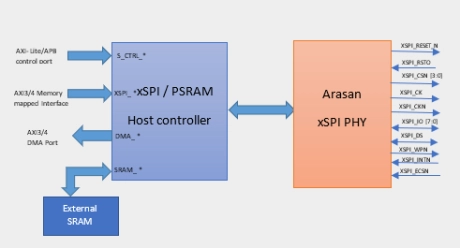

xSPI PHY

- The xSPI PHY is designed to work with both the xSPI/PSRAM and the xSPI master host controller IPs. When coupled with the ACS xSPI PHY, the combined IPs are able to interact with SPI, Dual SPI, Quad SPI, Octal SPI, and xSPI devices at the full 200 MHz data rate.

- This includes both HyperRAM and HyperFlash protocols. Both single and dual data rate modes are supported. The xSPI Master controller IP supports flash devices, whereas the xSPI/PSRAM controller has been designed to support SRAM types of devices using the same interface.

-

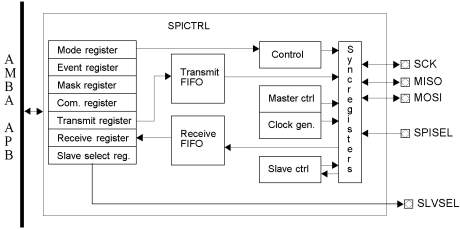

SPI Controller

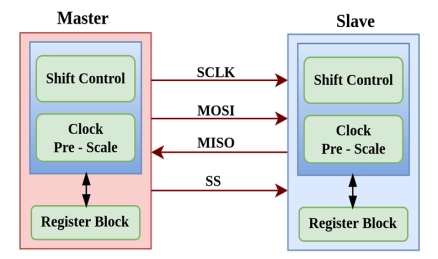

- The SPICTRL provides a link between the AMBA APB bus and the Serial Peripheral Interface (SPI) bus.

- Through registers mapped into APB address space the core can be configured to work either as a master or a slave.

-

SafeSPI - Function Controller

- The SafeSPI is a secure version of the SPI protocol that has been designed to provide enhanced security features, making it suitable for use in sensitive applications.

- Error detection through the SPI is crucial in ensuring the safety and reliability of airplanes.

- The SafeSPI protocol ensures that all data transfer is performed securely, preventing any unauthorized access to the transmitted data.

-

SPI - Function Controller

- The SPI protocol specification supports high speed data transfer as per the peripheral specification, making it ideal for high - performance applications that require fast data transfer rates.

-

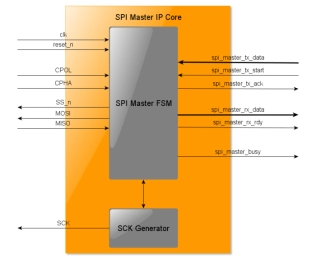

SPI Master DO-254 IP Core

- The SPI Master IP Core implements an SPI Master fully compliant to the SPI Standard (Motorola’s M68H11 Reference Manual).

- The Serial Peripheral Interface (SPI) bus is a synchronous serial communication interface specification used for short distance communication, primarily in embedded systems.