Transform IP

Welcome to the ultimate Transform IP hub! Explore our vast directory of Transform IP

All offers in

Transform IP

Filter

Compare

259

Transform IP

from

20

vendors

(1

-

10)

-

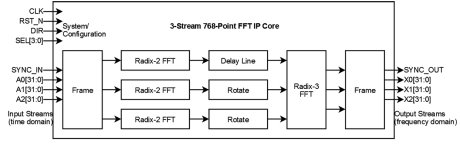

MixedRadix FFT IP Core

- The MixedRadix FFT IP Core uses a modular combination of radix2, 3, 5, and 7 Fast Fourier Transform (FFT) pipelined engines to provide discrete transforms on data frames or continuous data streams, with sample rate up to the maximum clock frequency.

- The engines are arranged to provide the most beneficial resource usage and data ordering for the system.

-

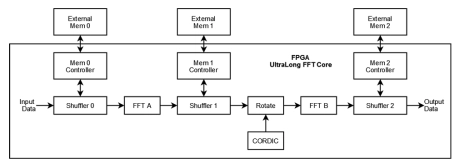

UltraLong FFT

- The UltraLong FFT IP Core uses an efficient Fast Fourier Transform (FFT) algorithm to provide multimillion-point discrete transforms on data frames or continuous data streams.

- This structure utilizes state-of-the-art off-chip memory technology and N1- and N2-length pipelined radix-2 FFT engines with an additional rotation stage to perform N=N1xN2 transform lengths, from 1K to 64M points.

-

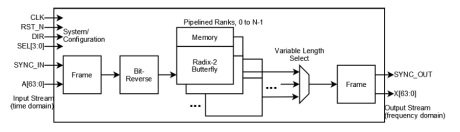

Pipelined Floating Point FFT IP Core

- Any radix-2 length

- Variable length option for runtime per-transform length select

- Clock rates to 400MHz in Virtex-5

- Fixed or floating point math

-

Fast Fourier Transform IP Core

- Supports forward and inverse complex FFT

- Supports transform length (N) from 23 to 2¹⁶

- Supports scaled or unscaled IFFT output

- Implemented as pipelined streaming IO architecture

-

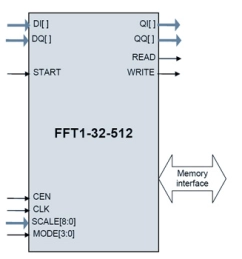

32-512 Point Streaming FFT Core

- Supports 32/64/128/256/512-point complex FFT and IFFT and can switch dynamically

- Inputs and outputs data in the natural order

- Throughput of 1 sample (In-phase I + quadrature Q) per 4 clocks; no-gap processing of the input data

- Parameterized bit width.

-

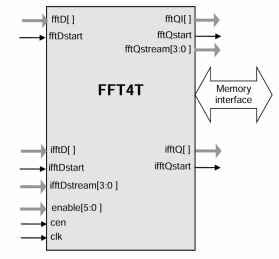

128-Point FFT/IFFT IP Core

- The FFT4T core implements a 128 point complex FFT and IFFT over 12 data streams in hardware. It runs at the clock frequency four times higher than the insput sampling frequency.

- FFT4T core is a specialized FFT/IFFT processor intended for a situation where an RF signal is recieved over multiple channels in parallel and its filtering is to be performed in the frequency domain. The core fits nicely into, for example, a multichannel GPS system.

-

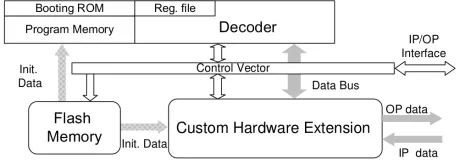

ASIP-2 Programmable Filter Engine

- Platform to design Application Specific Instruction Set Processors (ASIPs).

- Ideal for supporting multi-standard systems.

- Supports a wide range of complex DSP functions

- The ASIP2 performs Fast Fourier Transform (FFT) to convert time domain signals to frequency domain signals for further processing. It supports FFT sizes from 4 to 8K.

-

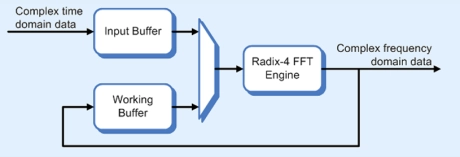

General-purpose FFT core

- The FFT is factored into Radix-4 Butterfly operations. When an odd power of two is required, a small radix-2 “follower” stage performs the final iteration. The radix-2 stage does not require a full complex rotator so its cost is minimal.

- The Radix-4 Engine fetches one complex word of data each clock cycle. Four interleaved data words are collected then applied to the t0-t3 inputs. On successive clock cycles the engine calculates the four frequency domain outputs f0-f3. These are then stored back into the Working Buffer.

-

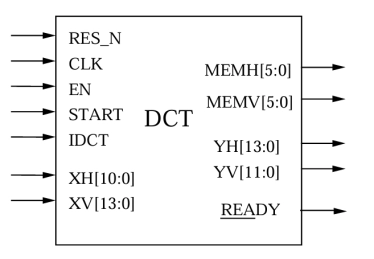

Discrete Cosine Transform

- This core can perform the two dimensional Discrete Cosine Transform (DCT) and its inverse (IDCT) on an 8x8 block of samples.

- The simple, fully synchronous design allows for fast operation while maintaining a low gate count.

- It offers high performance and many features to meet your multimedia, digital video and digital printing applications

-

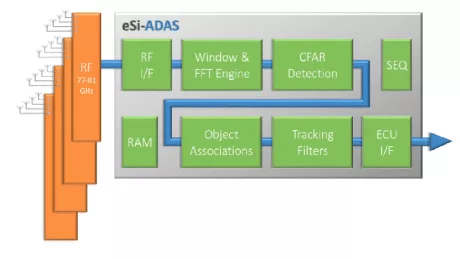

Radar processing IP suite for Advanced Driver Assistance Systems

- The eSi-ADAS™ is a suite of radar accelerator IP including a complete Radar co-processor engine, they enhance the overall performance and capabilities of radar systems for automotive, drone and UAV applications that require fast and responsive situational awareness.

- The IP has been licensed to some of the leading automotive Tier 1 and Tier 2 suppliers and is in production vehicles.