12-bit 250MHz Decimation filter with 43 taps

The ODT-DSP-DEC-43T250M-T16 is a 12-bit 250MHz Decimation filter with 43 taps in a 12/16nm CMOS process.

Overview

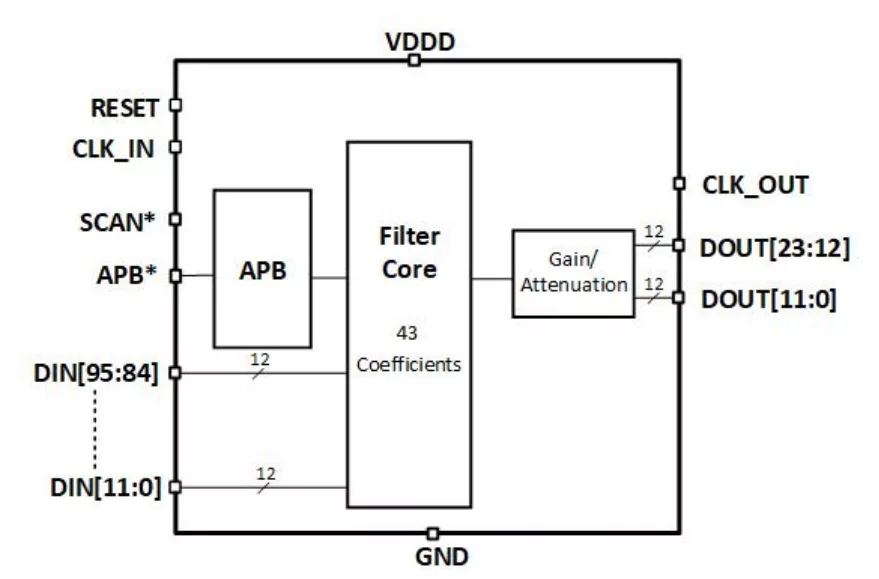

The ODT-DSP-DEC-43T250M-T16 is a 12-bit 250MHz Decimation filter with 43 taps in a 12/16nm CMOS process.

The 43 Tap Decimation filter reduces the output data rate (fDOUT) by a factor of 4 compared to the input data rate (fDIN) from an ADC.

Programmable coefficients allow customization of the filter characteristics for various application needs.

The filter is designed with programmable gain/attenuation settings for the output. Filter area is optimized by reducing the number of multipliers.

Filter has bypass mode option where DIN is directly passed to DOUT.

Key features

- Programmable Coefficients

- Programmable gain/attenuation at the output

- 4X Decimation Factor

- 12-Bit operation

Block Diagram

Applications

- High speed data acquisition systems

- RF systems

- DSP applications

What’s Included?

- Datasheet

- Hard Macro (GDSII and CDL)

- Verilog Model

- Liberty Files

- Power Spreadsheet

- Physical Abstract (LEF)

- Integration and Customer Support

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 16nm | 16nm 160 nm | — |

Specifications

Identity

Provider

Learn more about Filters Transforms IP core

No size fits all for signal processing on FPGA (RF Engines)

Employing general-purpose processors for radio DSP

Do's and Don'ts of Architecting the Right FPGA Solution for DSP Design

10 FPGA Design Techniques You Should Know

How to implement double-precision floating-point on FPGAs

Frequently asked questions about Filters and Transforms IP cores

What is 12-bit 250MHz Decimation filter with 43 taps?

12-bit 250MHz Decimation filter with 43 taps is a Filters Transforms IP core from Omni Design Technologies, Inc. listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Filters Transforms?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Filters Transforms IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.