FPGA-Accelerated RISC-V ISA Extensions for Efficient Neural Network Inference on Edge Devices

By Arya Parameshwara, Santosh Hanamappa Mokashi

Department of Electronics and Communication, PES University, Bangalore, India

Abstract

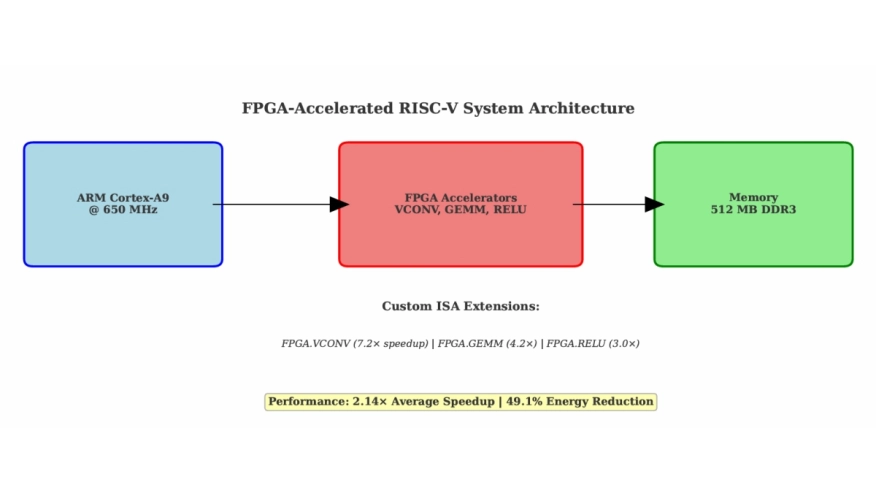

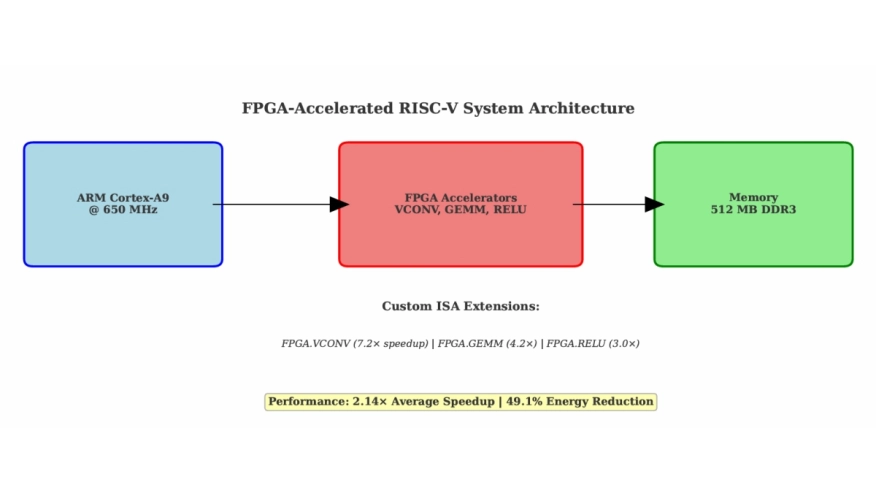

Edge AI deployment faces critical challenges balanc ing computational performance, energy efficiency, and resource constraints. This paper presents FPGA-accelerated RISC-V instruction set architecture (ISA) extensions for efficient neural network inference on resource-constrained edge devices. We introduce a custom RISC-V core with four novel ISA extensions (FPGA.VCONV, FPGA.GEMM, FPGA.RELU, FPGA.CUSTOM) and integrated neural network accelerators, implemented and validated on the Xilinx PYNQ-Z2 platform.

Edge AI deployment faces critical challenges balanc ing computational performance, energy efficiency, and resource constraints. This paper presents FPGA-accelerated RISC-V instruction set architecture (ISA) extensions for efficient neural network inference on resource-constrained edge devices. We introduce a custom RISC-V core with four novel ISA extensions (FPGA.VCONV, FPGA.GEMM, FPGA.RELU, FPGA.CUSTOM) and integrated neural network accelerators, implemented and validated on the Xilinx PYNQ-Z2 platform.

The complete system achieves 2.14× average latency speedup and 49.1% energy reduction versus an ARM Cortex-A9 software baseline across four benchmark models (MobileNet V2, ResNet 18, EfficientNet Lite, YOLO Tiny). Hardware implementation closes timing with +12.793ns worst negative slack at 50MHz while using 0.43% LUTs and 11.4% BRAM for the base core and 38.8% DSPs when accelerators are active. Hardware verification confirms successful FPGA deployment with verified 64KB BRAM memory interface and AXI interconnect functionality.

All performance metrics are obtained from physical hardware measurements. This work establishes a reproducible framework for ISA-guided FPGA acceleration that complements fixed function ASICs by trading peak performance for programmability.

Index Terms — RISC-V, ISA extensions, FPGA acceleration, neural networks, edge computing, energy efficiency, hardware software co-design

To read the full article, click here

Related Semiconductor IP

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

- Low-Power Embedded RISC-V Processor

- Enhanced-Processing Embedded RISC-V Processor

- Vector-Capable Embedded RISC-V Processor

- Compact Embedded RISC-V Processor

Related Articles

- MultiVic: A Time-Predictable RISC-V Multi-Core Processor Optimized for Neural Network Inference

- Bare-Metal RISC-V + NVDLA SoC for Efficient Deep Learning Inference

- VMXDOTP: A RISC-V Vector ISA Extension for Efficient Microscaling (MX) Format Acceleration

- Pyramid Vector Quantization and Bit Level Sparsity in Weights for Efficient Neural Networks Inference

Latest Articles

- RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

- Emulation-based System-on-Chip Security Verification: Challenges and Opportunities

- A 129FPS Full HD Real-Time Accelerator for 3D Gaussian Splatting

- SkipOPU: An FPGA-based Overlay Processor for Large Language Models with Dynamically Allocated Computation

- TensorPool: A 3D-Stacked 8.4TFLOPS/4.3W Many-Core Domain-Specific Processor for AI-Native Radio Access Networks