Uncertainty-Guided Live Measurement Sequencing for Fast SAR ADC Linearity Testing

By Thorben Schey 1, Khaled Karoonlatifi 2, Michael Weyrich 1 and Andrey Morozov 1

1 Institute of Industrial Automation and Software Engineering, University of Stuttgart, Stuttgart, Germany

2 Advantest Europe GmbH, Boblingen, Germany

Abstract

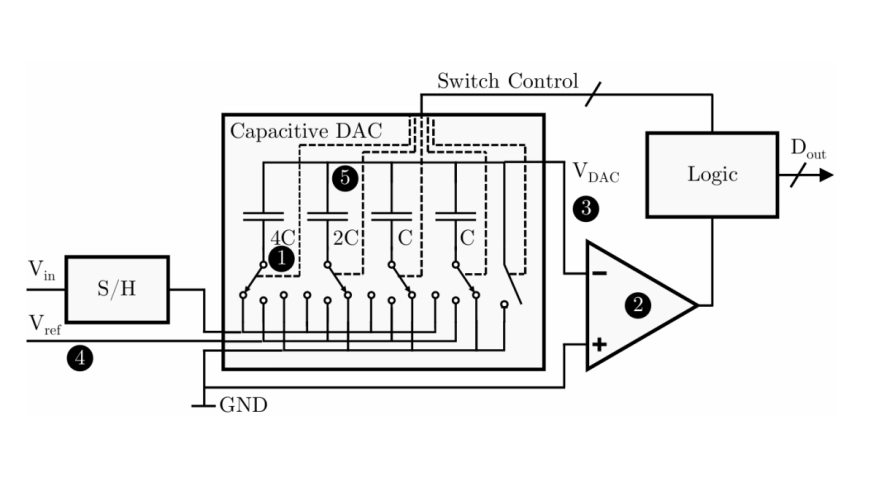

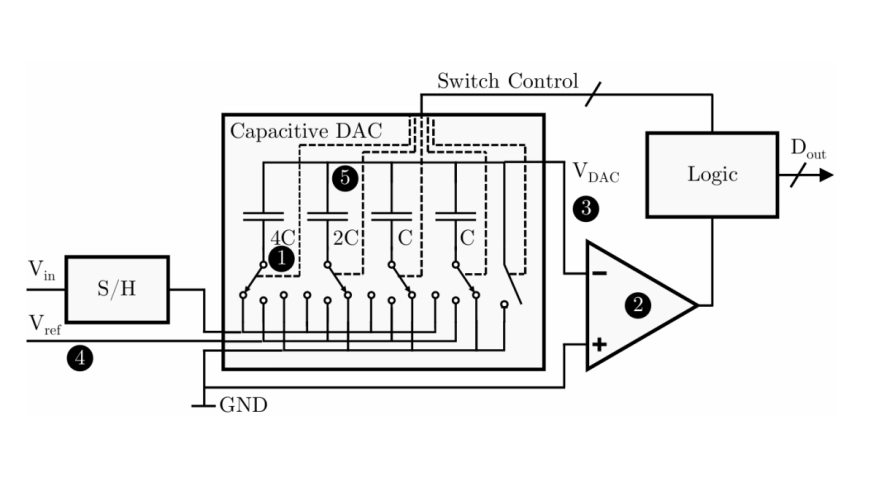

This paper introduces a novel closed-loop testing methodology for efficient linearity testing of high-resolution Successive Approximation Register (SAR) Analog-to-Digital Converters (ADCs). Existing test strategies, including histogram-based approaches, sine wave testing, and model-driven reconstruction, often rely on dense data acquisition followed by offline post-processing, which increases overall test time and complexity. To overcome these limitations, we propose an adaptive approach that utilizes an iterative behavioral model refined by an Extended Kalman Filter (EKF) in real time, enabling direct estimation of capacitor mismatch parameters that determine INL behavior. Our algorithm dynamically selects measurement points based on current model uncertainty, maximizing information gain with respect to parameter confidence and narrowing sampling intervals as estimation progresses. By providing immediate feedback and adaptive targeting, the proposed method eliminates the need for large-scale data collection and post-measurement analysis. Experimental results demonstrate substantial reductions in total test time and computational overhead, highlighting the method's suitability for integration in production environments.

This paper introduces a novel closed-loop testing methodology for efficient linearity testing of high-resolution Successive Approximation Register (SAR) Analog-to-Digital Converters (ADCs). Existing test strategies, including histogram-based approaches, sine wave testing, and model-driven reconstruction, often rely on dense data acquisition followed by offline post-processing, which increases overall test time and complexity. To overcome these limitations, we propose an adaptive approach that utilizes an iterative behavioral model refined by an Extended Kalman Filter (EKF) in real time, enabling direct estimation of capacitor mismatch parameters that determine INL behavior. Our algorithm dynamically selects measurement points based on current model uncertainty, maximizing information gain with respect to parameter confidence and narrowing sampling intervals as estimation progresses. By providing immediate feedback and adaptive targeting, the proposed method eliminates the need for large-scale data collection and post-measurement analysis. Experimental results demonstrate substantial reductions in total test time and computational overhead, highlighting the method's suitability for integration in production environments.

Index Terms — ADC linearity testing, SAR ADC, adaptive test strategy, behavioral modeling, Extended Kalman Filter, real-time estimation, analog mixed-signal

To read the full article, click here

Related Semiconductor IP

- SAR ADC

- SAR ADC

- 14-bit 12.5MSPS SAR ADC - Tower 65nm

- 10-bit SAR ADC - XFAB XT018

- Low-power 8-bit 80 MHz SAR ADC

Related Articles

- UWB Time-interleaved ADC exploiting SAR

- Linearity Analysis of Source-Degenerated Differential Pairs for Wireline Applications

- Design and Implementation of Test Infrastructure for Higher Parallel Wafer Level Testing of System-on-Chip

- FastPath: A Hybrid Approach for Efficient Hardware Security Verification

Latest Articles

- RISC-V Functional Safety for Autonomous Automotive Systems: An Analytical Framework and Research Roadmap for ML-Assisted Certification

- Emulation-based System-on-Chip Security Verification: Challenges and Opportunities

- A 129FPS Full HD Real-Time Accelerator for 3D Gaussian Splatting

- SkipOPU: An FPGA-based Overlay Processor for Large Language Models with Dynamically Allocated Computation

- TensorPool: A 3D-Stacked 8.4TFLOPS/4.3W Many-Core Domain-Specific Processor for AI-Native Radio Access Networks