relOBI: A Reliable Low-latency Interconnect for Tightly-Coupled On-chip Communication

By Michael Rogenmoser, Angelo Garofalo and Luca Benini (ETH Zurich)

Abstract

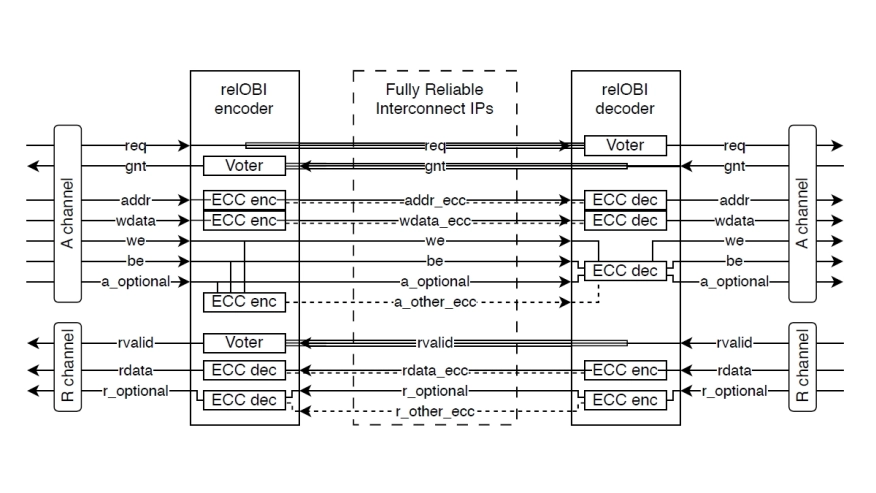

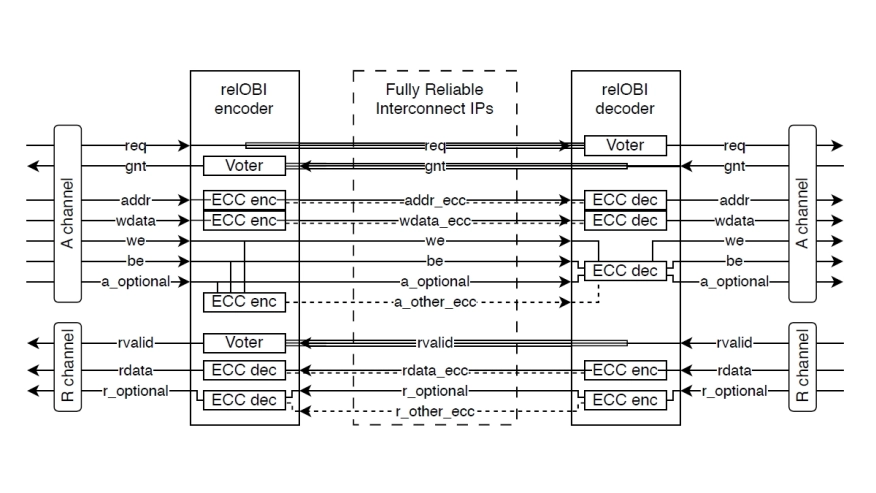

On-chip communication is a critical element of modern systems-on-chip (SoCs), allowing processor cores to interact with memory and peripherals. Interconnects require special care in radiation-heavy environments, as any soft error within the SoC interconnect is likely to cause a functional failure of the whole SoC. This work proposes relOBI, an extension to Open Bus Interface (OBI) combining triple modular redundancy (TMR) for critical handshake signals with error correction codes (ECC) protection on other signals for complete reliability. Implementing and testing a fully reliable crossbar shows improved reliability to injected faults from a vulnerability of 34.85 % to 0 % compared to a reference design, with an area increase of 2.6x and 1.4x timing impact. The area overhead is 1.8x lower than that reported in the literature for fine-grained triplication and voting.

On-chip communication is a critical element of modern systems-on-chip (SoCs), allowing processor cores to interact with memory and peripherals. Interconnects require special care in radiation-heavy environments, as any soft error within the SoC interconnect is likely to cause a functional failure of the whole SoC. This work proposes relOBI, an extension to Open Bus Interface (OBI) combining triple modular redundancy (TMR) for critical handshake signals with error correction codes (ECC) protection on other signals for complete reliability. Implementing and testing a fully reliable crossbar shows improved reliability to injected faults from a vulnerability of 34.85 % to 0 % compared to a reference design, with an area increase of 2.6x and 1.4x timing impact. The area overhead is 1.8x lower than that reported in the literature for fine-grained triplication and voting.

To read the full article, click here

Related Semiconductor IP

- Network-on-Chip (NoC)

- NoC Verification IP

- NoC System IP

- Non-Coherent Network-on-Chip (NOC)

- Coherent Network-on-Chip (NOC)

Related Articles

- A 'network-centric' approach to on-chip interconnect

- On-Chip Interconnect Costs Spawn Research

- Fault Injection in On-Chip Interconnects: A Comparative Study of Wishbone, AXI-Lite, and AXI

- CompactPCI Interconnect Spec To Be Enhanced

Latest Articles

- An FPGA-Based SoC Architecture with a RISC-V Controller for Energy-Efficient Temporal-Coding Spiking Neural Networks

- Enabling RISC-V Vector Code Generation in MLIR through Custom xDSL Lowerings

- A Scalable Open-Source QEC System with Sub-Microsecond Decoding-Feedback Latency

- SNAP-V: A RISC-V SoC with Configurable Neuromorphic Acceleration for Small-Scale Spiking Neural Networks

- An FPGA Implementation of Displacement Vector Search for Intra Pattern Copy in JPEG XS