Beyond design automation: How we manage processor IP variants with Codasip Studio

If you’ve been following us at Codasip, you know we’re all about enabling Custom Compute. The power to shape processor hardware to get the best out of your software is, as we see it, key to standing out and getting that crucial edge in performance, power, and area. A big part of what we offer here is Codasip Studio, our processor design toolset, and its architectural language, CodAL. Many engineers know Studio for its powerful ability to generate both a Hardware Development Kit (HDK) and a Software Development Kit (SDK) – that’s compilers, debuggers, models, the whole lot – all from one CodAL description. That alone is a huge time saver, especially when you’re innovating with your own custom instructions.

But today, I want to take you deeper into another side of Codasip Studio that we find incredibly powerful, especially when we’re managing processor IP that comes in many different flavors. It’s something that might not be immediately obvious but is critical for serious processor development. Management of configurable processor IP.

Configurable IP headaches? How Studio takes them away

Creating highly configurable processor cores, or whole families of cores for different applications, offers tremendous flexibility. However, anyone who’s worked on such IP knows it can bring its own set of engineering headaches. One of the primary challenges is ensuring that the specific set of features and parameters you pick for a particular IP variant is correctly and consistently applied everywhere. It’s not just about the RTL code; your compiler needs to understand any custom instructions active in that variant, your debugger needs to be aware of the specific hardware features, and your simulation models have to perfectly mirror the configured hardware. A mismatch in any of these areas, perhaps due to providing slightly different configuration inputs to different tools, can lead to incredibly frustrating debug sessions. We’ve all been there, chasing bugs that stem from inconsistent setups.

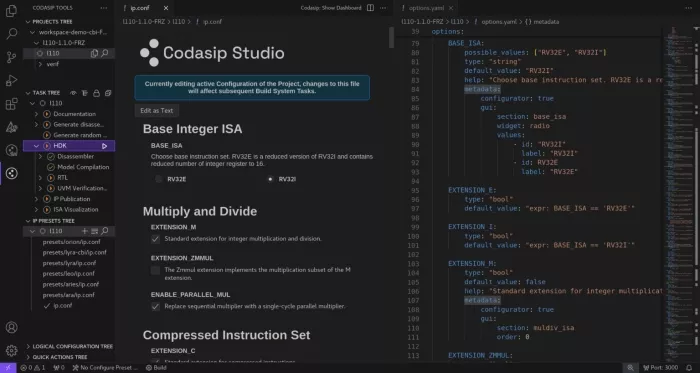

This is precisely where Codasip Studio’s integrated configuration system steps in to provide a robust solution. At its core, Studio allows for two main types of configuration to ensure everything lines up. First, there’s the tooling and generator configuration. These settings are generally relevant for any IP you’re working on with Studio and dictate how the outputs – like the simulator, compiler, or the RTL itself – are generated. Think of these as the knobs that control the generation process itself.

Building on top of this, and crucial for IP-specific tailoring, is what we call the options system. This is a powerful meta-language, typically managed within a YAML file, where you, as the IP designer, can define a whole set of configuration options that are unique and relevant to your specific IP. These options are then directly reflected in the CodAL description of your processor as variables you can use throughout your design. What makes this particularly effective is that these IP-specific options can also be used to drive the tooling and generator configurations I mentioned earlier. This creates a true single source of truth, all managed from one configuration approach, ensuring that your entire toolset and hardware are perfectly in sync with the chosen IP variant. No more crossed wires.

With such a system in place, the next logical step is to ensure the configurations themselves are robust. Studio allows you, the IP designers, to embed additional context into these options. For each option, you can, among other, define:

- Legal values: Specifying the permissible range or set of values prevents someone from choosing a combination the design wasn’t tested or verified for.

- Dependencies: You can define relationships between various options, ensuring that selecting one option correctly enables or restricts others. This stops illogical or unsupported hardware states from ever being configured.

- Calculated values: Some parameters might need to be derived based on other choices. The options system allows you to define these, so they are automatically computed, further reducing manual input and potential errors.

This level of detailed control means each processor variant configuration can be precisely defined, easily backed up, and perfectly reproduced in the future. Your team can maintain numerous such configuration files within the CodAL project, representing distinct variants of your IP, and switch between them with confidence, knowing Studio will generate a consistent set of deliverables every time.

Now, let’s talk about another common pain point with highly configurable IP: “dead code”. If your IP offers many optional features, any specific variant will likely only use a subset of them. If the RTL for all those unused features still gets generated, it can create significant problems during verification. Your team might spend considerable effort trying to achieve coverage on this inactive logic or, more commonly, formally “waiving” it. This isn’t just time-consuming; it’s risky. An incorrect assumption could lead to genuinely active logic being waived, potentially masking bugs that could even lead to a non-functioning tape-out. Studio addresses this elegantly. Because the optional functionality is captured conditionally in CodAL, if a feature isn’t enabled through the options system for a specific variant, the RTL representing that part of the design simply isn’t generated by Studio. The RTL you take to verification is precisely the RTL for the configuration you intend, making your verification process cleaner, faster, and more reliable.

Our secret sauce: Building configurable processor families with Studio

So, how do we leverage this powerful system ourselves at Codasip? The truth is, these IP management and configuration capabilities are absolutely central to how we build our own processor IP. Our RISC-V cores are designed to be highly configurable to meet a diverse spectrum of application needs, and we achieve this by making each core family a CodAL project in Studio. Each project effectively represents an entire family of processors, with specific members of that family being instantiated simply by applying different configurations.

A prime example of this is our 100 Family processor IP. This family is a testament to what robust configurability can achieve, covering use-cases from simple, area-optimized finite state machine replacements all the way to mid-range DSP processors capable of handling more demanding signal processing tasks. All these distinct processors, with their varied performance points and feature sets, are derived from the same configurable CodAL base, all managed, built, and verified using Codasip Studio.

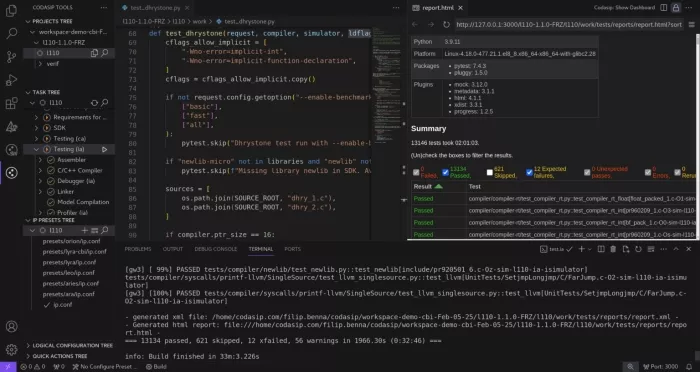

But managing the RTL and SDK is only part of the story. For efficient IP development, automation is key. That’s why, alongside the core processor logic, we embed significant automation directly into our CodAL projects using two primary frameworks:

- Our build system, which is a task-based automation framework, helps us manage complex build sequences.

- Our test suite allows us to create and manage extensive test campaigns.

What’s really powerful is that any part of Studio is designed to be extensible. This means our engineers—and our customers—can define their own custom automation tasks or tests and seamlessly integrate them into the development flow. These can be registered to appear as additional task buttons right inside the Studio GUI – which, by the way, is our set of custom extensions for Visual Studio Code, providing a modern integrated environment for both hardware and software development. Alternatively, these automations can be set up to run automatically in response to specific events, like running a set of regression tests every time new RTL is generated. And, crucially, all of this automation can be controlled by the same configuration system. So, for example, when we generate RTL for a particular processor variant, only the tests valid and relevant for that specific core configuration are executed, saving time and focusing verification effort where it’s most needed. Our ultimate goal is for Studio to be the only toolset you’ll need for the comprehensive development of your IP and the applications that will run on it.

And when it’s time to deliver a specific configuration to a customer, this sometimes involves creating a package containing the precise RTL of that processor variant and its correctly configured SDK. This automated package creation is another piece of the puzzle we manage from within the CodAL project and can run directly from Studio, whether we’re using the GUI or driving it via command-line for our larger build systems.

Your turn: Use Studio to architect your own custom IP

The good news is that this comprehensive environment, with all its sophisticated IP management and automation features, isn’t just for our internal teams at Codasip. We, the Codasip Studio team, built these capabilities to be robust and flexible enough for our own demanding IP teams, which means they are thoroughly production-proven and ready for your design challenges too.

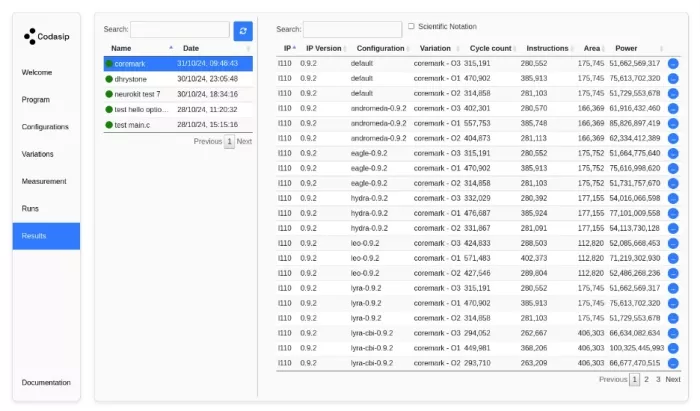

These same Studio features are available to you, our customers. You can leverage them when you’re licensing and configuring Codasip’s own IP, like the versatile 100 Family or high-performance 700 Family. Studio will allow you to explore different core configurations, benchmark them with your specific software workloads, and ultimately identify the optimal hardware setup that meets your product’s unique requirements. As you can imagine by now, we have a tool helping with that configuration selection process as well. We may dedicate a blog post to it next time.

More than that, if you’re embarking on designing your own unique, configurable processor IP – perhaps starting from one of our cores or building something entirely new – Codasip Studio provides this same powerful system to manage your custom configurations, ensure consistency across your hardware and software, and streamline your entire development and verification process.

So, while the headline feature of Studio might be the automated generation of HDKs and SDKs from a single CodAL source, it’s this deep, integrated IP management and automation system that truly empowers you to handle the complexity of today’s configurable designs. It’s how we aim to help you go beyond the standard, to truly architect your ambition, giving you the detailed control and comprehensive tools you need to design different and build something uniquely better.

Related Semiconductor IP

- 32 Bit - Embedded RISC-V Processor Core

- 32 bit - Compact RISC-V Processor Core

- Compact RISC-V Processor - 32 bit, 3-stage pipeline, 32 registers

- 32 Bit - Embedded RISC-V Processor Core

- RISC-V Debug & Trace IP

Latest Blogs

- Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

- Why Your Next Smartphone Needs Micro-Cooling

- Teaching AI Agents to Speak Hardware

- SOCAMM: Modernizing Data Center Memory with LPDDR6/5X

- Bridging the Gap: Why eFPGA Integration is a Managed Reality, Not a Schedule Risk